今天小编要和大家分享的是D触发器脉冲特性 D触发器工作原理,接下来我将从D触发器的脉冲特性,D触发器的工作原理,D触发器常用芯片型号,D触发器的VHDL语言设计,用D触发器构成JK触发器,这几个方面来介绍。

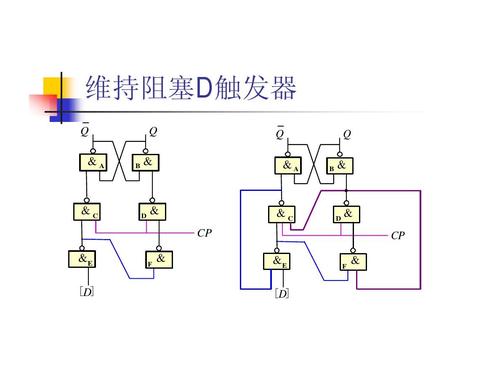

D触发器也称为维持-阻塞边沿D触发器,其与普通触发器的区别在于:电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

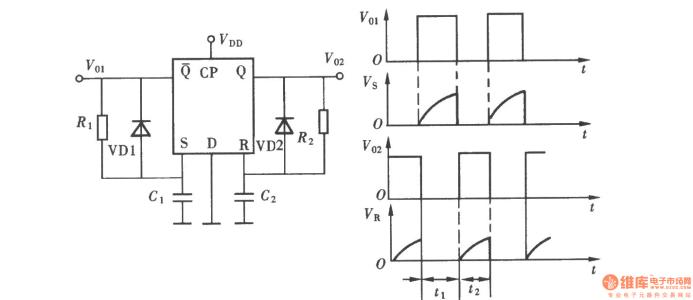

D触发器的脉冲特性

1.建立时间:

由维持阻塞触发器的电路可见,由于Cp信号是加到门G3和G4上的,因而在Cp上升沿到达之前门G5和G6输出端的状态必须稳定地建立起来。输入信号到达D端以后,要经过一级门电路的传输延迟时间G5的输出状态才能建立起来,而G6的输出状态需要经过两级门电路的传输延迟时间才能建立,因此D端的输入信号必须先于Cp的上升沿到达,而且建立时间应满足:tset≥2tpd。

2.保持时间:

为实现边沿触发,应保证Cp=1期间门G5的输出状态不变,不受D端状态变化的影响。为此,在D=0的情况下,当Cp上升沿到达以后还要等门G3输出的低电平返回到门G5的输入端以后,D端的低电平才允许改变。因此输入低电平信号的保持时间为tHL≥tpd。在D=1的情况下,由于Cp上升沿到达后G4的输出将G3封锁,所以不要求输入信号继续保持不变,故输入高电平信号的保持时间tHH=0。

3.传输延迟时间:

从Cp上升沿到达时开始计算,输出由高电平变为低电平的传输延迟时间tpHL和由低电平变为高电平的传输延迟时间tpLH分别是:tpHL=3tpdtpLH=2tpd

4.最高时钟频率:

为保证由门G1~G4组成的同步RS触发器能可靠地翻转,Cp高电平的持续时间应大于tpHL,所以时钟信号高电平的宽度tWH应大于tpHL。而为了在下一个Cp上升沿到达之前确保门G5和G6新的输出电平得以稳定地建立,Cp低电平的持续时间不应小于门G4的传输延迟时间和tset之和,即时钟信号低电平的宽度tWL≥tset+tpd

最后说明一点,在实际集成触发器中,每个门传输时间是不同的,并且作了不同形式的简化,因此上面讨论的结果只是一些定性的物理概念。其真实参数由实验测定。在考虑建立保持时间时,应该考虑时钟树向后偏斜的情况,在考虑建立时间时应该考虑时钟树向前偏斜的情况。在进行后仿真时,最大延迟用来检查建立时间,最小延时用来检查保持时间。

D触发器的工作原理

工作过程如下:

1.Cp=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D非,Q6=Q5非=D。

2.当Cp由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5非=D,Q4=Q6非=D非。由基本RS触发器的逻辑功能可知,Q=Q3=D。

3.触发器翻转后,在Cp=1时输入信号被封锁。这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。因此,该触发器常称为维持-阻塞触发器。总之,该触发器是在Cp正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。与主从触发器相比,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度。

D触发器常用芯片型号

74HC7474LS90双D触发器74LS74

74LS364八D触发器(三态)

7474、74H74、74F74、74ALS74、74L74、74LS74A、74S74、74HC73、74C74双D型正沿触发器(带预置和清除端)

74174、74LS174、74F174、74ALS174、74S174、74HC174、74C174 六D型触发器(带清除端)

74175、74LS175、74F175、74ALS175、74S175、74HC175、74C175四D型触发器(带清除端)

74273、74LS273、74S273、74F273、74ALS273、74HC273八D型触发器(带清除端)

74LS377、74F377、74S3777 八D触发器

74LS378、74F378、74S378、74HC378 六D触发器

74LS379、74F379、74S379、74HC379八D触发器

D触发器的VHDL语言设计

使用VHDL语言设计D触发器的程序:

LIBRARYieee;USEieee.std[_]logic[_]1164.all;

ENTITYdflipflopIS

pORT(D,C:INSTD[_]LOGIC;

Q:OUTSTD[_]LOGIC);

ENDdflipflop;

ARCHITECTUREBehaviorOFdflipflopIS

BEGIN

pROCESS(C)

BEGIN

IFC'EVENTANDC='1'

THEN

Q<=D;

ENDIF;

ENDpROCESS;

ENDBehavior;

使用VerilogHDL语言实现D触发器(带R、S端)

//门级

modulecfq(s,r,d,clk,q,qbar);

inputs,r,d,clk;

outputq,qbar;

wirena1,na2,na3,na4;

nand

nand1(na1,s,na4,na2),

nand2(na2,r,na1,clk),

nand3(na3,na2,clk,na4),

nand4(na4,na3,r,d),

nand5(q,s,na2,qbar),

nand6(qbar,q,r,na3);

endmodule

或

//行为级

moduledff[_]rs[_]async(clk,r,s,d,q);

inputclk,r,s,d;

outputq;

regq;

always@(posedgeclkorposedgerorposedges)

begin

if(r)q<=1'b0;

elseif(s)q<=1'b1;

elseq<=d;

end

endmodule

用D触发器构成JK触发器

D触发器配上适当的组合逻辑电路,可实现JK触发器的功能。

设计原理:

对于JK触发器有:

Qn+1=JQn+KQn

对于D触发器有:

Qn+1=D

而D=Y

所以Qn+1=Y

Y=JQn+KQn

可根据此式设计转换电路。

转换原理图如下图所示:

关于D触发器,电子元器件资料就介绍完了,您有什么想法可以联系小编。