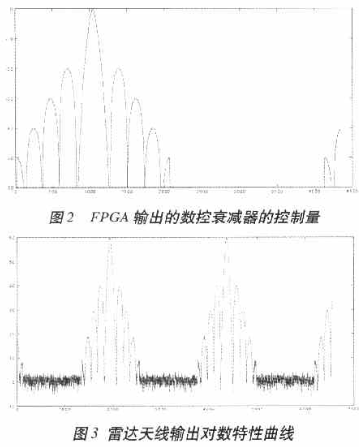

由DDS1输出的雷达信号经放大滤波后送给数控衰减器进行雷达天线扫描的调制,输出具有雷达天线包络的信号。数控衰减器的衰减范围为65dB,可控位数为12bit,最小步进0.5dB。图2所示为FPGA送给数控衰减器的控制量,系统要求干扰机接收信号的动态范围为60dB,因此衰减控制量的最大差值为60 dB。由于天线图的周期太长,为了便于观测,可以对输出的天线图进行A/D采样,采样后如图3所示。横坐标表示采样点,纵坐标为对幅值求对数后的量化值。该图即为天线的包络,读图可以知道天线主瓣与旁瓣的dB差值,主瓣与第四旁瓣的差值为50 dB。外时钟CLK信号是板内时钟经过时钟驱动芯片送往前面板的SMA头输出,可以提供给雷达模拟器处理板和回波模拟器处理板使用。

模块B:完成中频上的正交检波,对雷达回波中频信号和干扰中频信号合成后的信号进行检波,本振信号由DDS2的输出提供,即F1_out和F2_out,分别与F1_in和F2_in相连。该模块设计了两路是因为要对雷达分别进行主天线和辅助天线的处理。对DDS送来的主天线和辅助天线的合成信号分别进行正交检波,输出两路I、Q信号送给雷达模拟器。

模块C:对雷达回波模拟器产生的基带正交信号进行调制,调制到具有捷变功能的中频本振上,本振信号F3_in由DDS2经过功分器输出的F3_out提供,本振变化的规律与DDS1产生的雷达发射信号的变化一致。中频调制后的信号经过功分器分成两路,再经过压控振荡器,分别对两路信号进行天线调制,其中一路作为主天线回波信号,另一路作为辅助天线回波信号。压控衰减器的控制量由雷达回波模拟器经由前面板的Con1和Con2提供。