1 总体结构与基本工作原理

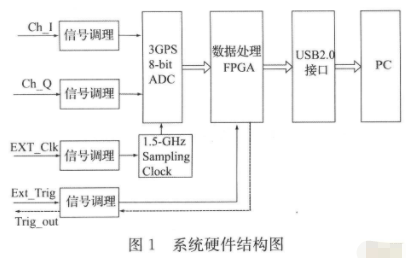

图1所示为本系统整体硬件框图,数字信号中和器主要由前端信号调理模块、射频采集模块、高速时钟产生模块、FPGA模块、USB接口模块等部分组成。其中信号调理模块主要由前置放大器ERA_1+和变压器ADTL2_18组成。射频采集模块主要由ADC08D1500及相关外围电路组成。高速时钟产生模块由ADI公司的时钟产生芯片AD9517-4组成。数据处理及控制模块由XILINX VIR-TEX-4 SX35 FPGA及相关外围电路组成。USB2.0传输及控制模块由Cypress公司的CY7C68013及相关外围电路组成。

本数字信号中和器具有内、外触发两种工作模式。在内触发工作模式下,由系统自身产生触发(start)信号,并由触发通道输出电子引导脉冲信号,以引导质谱仪前端设备。而在外触发工作模式下,系统采集外触发信号的到达以作为转换的开始。

当射频采集模块工作在单边沿采样时,通道I和通道Q为独立的stop信号采集通道,最高采样率为1.5GSPS;当射频采集模块工作在双边沿采样时,通道I和通道Q只能有一个作为信号采集通道,最高采样率为3GSPS。以外触发、双边沿采样工作模式为例。触发通道采集外部触发信号以作为转换的时间起点,脉冲输入信号经前置放大、电平转换等信号调理后,进入射频采集模块。在双边沿工作模式下,高速时钟产生电路提供1.5GHz的采样时钟,从而可以使射频采集模块的最高采样率为3GSPS。ADC采样的结果分DI、DQ、DID、DQD4组8bit差分信号以DDR的形式传至FPGA,每组差分信号的速度为375MHz。FPGA启动相应逻辑,以50us为一周期,连续采集1s,每周期内持续采样时间20us。同时FPGA逻辑控制将不同周期内相同时刻的采样点对应相加,从而得到1s内累加的质谱图。最后FPGA通过USB控制逻辑将包含脉冲数量和到达时间信息的质谱图通过USB2.0接口传至PC以完成质谱图的绘制和后端信号处理。由于射频采集ADC的最高采样速率为3GSPS,即可达到333ps的时间分辨率。针对不同的应用背景,射频采集模块的时钟频率可调,调节范围为500MHz~3GHz,即时间分辨率为333ps~2ns可调。