实验结果和讨论

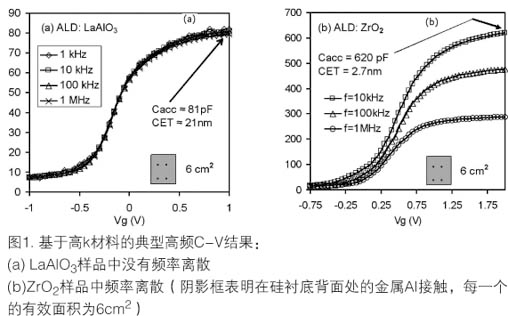

基于高k介质的典型C-V结果分别示于图1(a)和(b)。不管淀积方法、条件和材料如何,有时仍能得到频率离散。产生这一问题可能有三个因素:串联电阻影响,包括不完美的背接触;有损耗界面层的影响(~1nm原始SiO2);k值的频率相关影响。在讨论k值的频率相关影响前,必需充分研究串联电阻影响和有损耗界面层的影响。

串联电阻影响(通常是由于硅体电阻和不完美的背接触)的重要性在热SiO2 MOS电容中得到最好的展示,其中体电介质与硅衬底间的损耗界面层的影响是可以忽略的。SiO2中频率离散只有在衬底有效面积小的样品中观察到,如图2(a)所示。此外,对于没有Al背接触的小样品,尽管测量条件是同一的,测得的结果也不再重复,如图2(b)所示(闭合的符号)。这就破坏了测量方法的可靠性。

为了在任意测量时间和频率下对SiO2重建测得的C-V曲线,必须考虑可能由背接触不完美和硅串联电阻产生的“寄生”分量。然后对C-V曲线实施校正以得到它们的真实值。图3(a)是理想情况下的等效电路,可与实际测量模式比较,其中Cox代表SiO2栅介质的实际频率自主电容,Rs含有硅衬底的体电阻及不同接触电阻产生的量。背接触不完美也用电容Cp建模。CC、GC、Cm、Gm分别指已校正(没有“寄生”分量 Rs和Cp的影响)或测得的电容和电导。