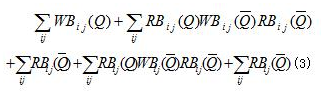

用这种测试算法检测存储芯片,可使每个存储单元都被访问。既能保证每个存储单元都能存储“1”和“0”数据,又能保证每个存储单元都受到周围其他单元的读“1”、读“0”和写“1”、写“0”的打扰。齐步法总的测试步数为:

式(3)中,W表示写操作,R表示读操作,Q表示“1”, 表示“0”。Bij表示存储器第i行j列的存储单元。如WBij(Q)就表示对第i行j列的存储单元进行写“1”操作所用的时间。

由式(3)可知,其测试步数共9N,且整个过程只需两次擦除操作,可见它是一种即快速又有效的方法。

4.3 移动变反法

移动变反测试法是按顺序变反每个地址存储单元数据的方法。它需要在变反前后读出每个存储单元的数据,而且,还必须借助于前进和后退的地址寻址序列产生地址跳跃,地址以20、21…、2n-1次方的增量变化(n是地址位数)。按照以上规律进行地址跳变后,再对每个地址进行三次操作:读、写和读即可完成一个循环。

以上操作的目的主要在于地址间产生有效相互打扰,但显然如果以整个芯片为单元进行上述操作需要多次擦除数据,因此对FLASH测试芯片应做如此改进:以扇区为单元完成操作。假设FLASH芯片有N个扇区,移动变反法的功能测试先要以“1”为背景图案写入全部存储单元。首先,在第一个扇区,对A0存储单元读出并验证是“1”,再将该存储单元改写成“0”,最后读出该存储单元的信息以证明新写入的“0”仍存于该存储单元中。第一扇区测试地址按有效位的阶20递增,对每个存储单元都要重复上述的读“1”,写“0”读“0”的操作过程,需要测试步长为3n(n为该扇区的存储单元数)才能使全部的存储单元都变成“0”。这次测试的地址序列是递增1的,即由地址最低位A0增加到最高位A(n-1),对A(n-1)存储单元进行读“1”,写“0”和读“0”验证。