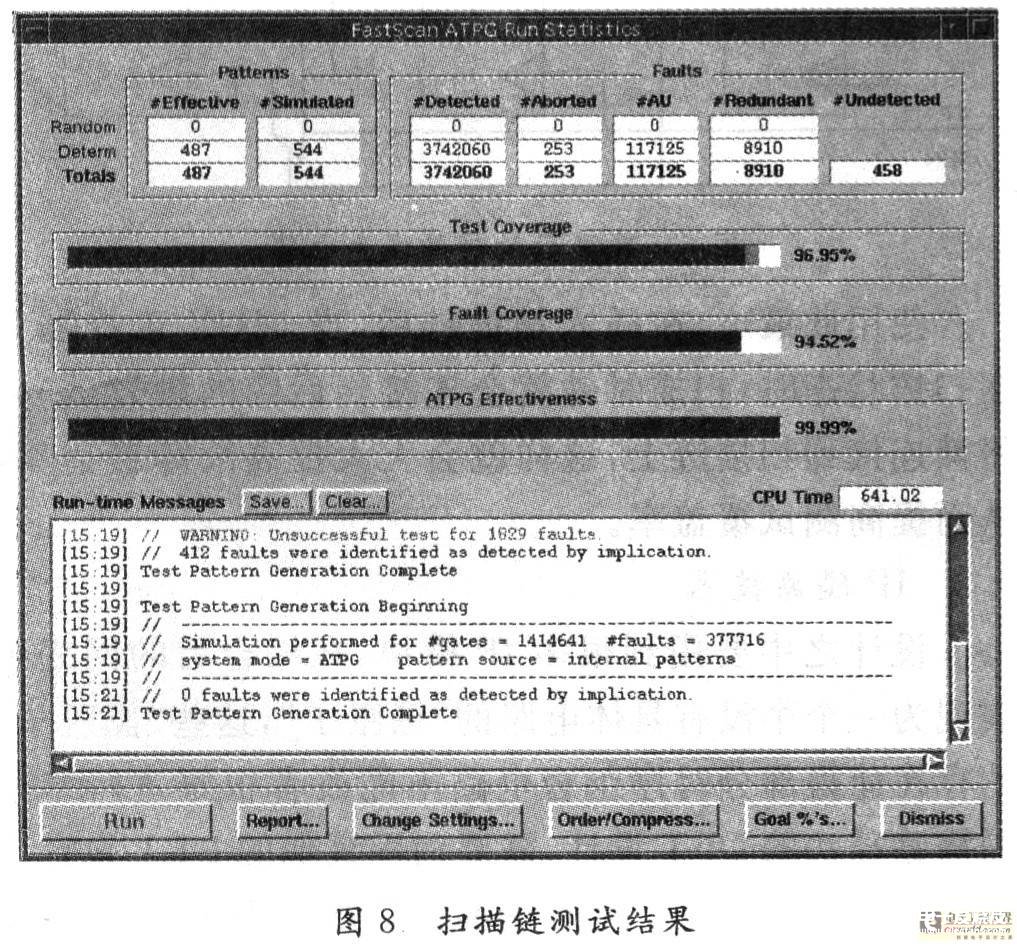

从图8可以看出,当采用了以上设计策略后测试覆盖率(test coverage)、故障覆盖率(fault coverage)和ATPG覆盖率分别达到96.95 9/6,94.52%和99.99%。

4.2 测试结果分析

在图8所示的测试结果数据栏中,左侧的数据栏中显示的是总共生成的测试向量以及有效的测试向量数目。右侧显示的是在扫描链测试过程中能够测出的各种故障数目,其中故障覆盖率F的计算公式为:

![]()

其中:不可测故障包括摒弃故障、固定故障、冗余故障等。本设计考虑了很多故障模型,其中就包括很多的固定故障类型(例如:芯片端口被锁定为固定值,无法检测到)计算到上述计算公式中,因此实际的不可测故障要比工具中统计的数字要少;通过以上分析可知,实际能达到的故障覆盖率要优于测试结果。

5 结 语

本文对一款约750万门的雷达数字处理芯片的电路进行基于扫描路径法的可测性设计,在设计中针对实际电路门数特别庞大的特点,采用时钟复用的技术,合理利用已经存在设计资源,使可测到的触发器数目大大增加;针对特殊的电路应用特殊的处理策略,增加了可测性设计的故障覆盖率。由试验结果可知,与未采用以上提到的设计策略相比,其最终的测试覆盖率得到很明显的提升,实现了设计策略应用的目标,最终也达到了设计的指标要求。

责任编辑:gt

关于测量仪表就介绍完了,您有什么想法可以联系小编。