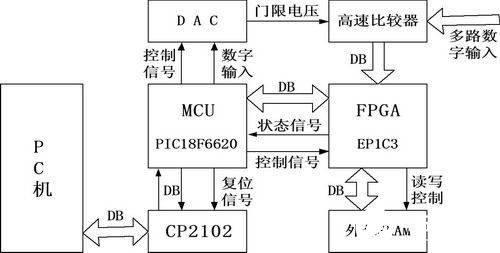

图1 系统功能框图

系统触发模块设计

触发模块是整个系统的核心部分,主要包括采样时钟选择模块、触发电平设置和触发电路三个部分。

采样时钟选择模块

时钟选择模块用于选择采样频率。可供选择的时钟源包括:外部时钟(由有源晶振提供)、单片机PWM模块产生的PWM时钟、外部时钟输入(由额外的设备提供)、以第N路数字信号输入作为采样时钟。

触发电平设置

触发电平用来确定系统正确识别采样信号的高低电平。该模块由串行数模转换器TLC5615和高速比较器LT1721构成。采样开始前,单片机向DAC发送触发电平数据,转换后的电平信号(范围从0~+5V)送入高速比较器。

触发电路

触发电路的作用是判断采样信号是否满足触发条件,并分别产生触发动作。当采集的信号满足用户设置的触发条件时,系统记录触发位置并产生触发信号通知上位机读取、显示采样数据。本次设计的触发电路具有三种可选的触发模式:立即触发、顺序触发和并行触发。

立即触发

当上位机向FPGA发出立即触发触发字和开始采样指令后,FPGA开始采样并立即产生触发信号。采样电路将采集到的信号存入外部的SRAM中,直至采集到规定的点数后停止采样,向上位机发出采样结束信号,通知其读取采样数据。此方式下读回的触发点位置为0。

顺序触发

该方式设置了一个8位的序列触发,只有当被测通道的信号按依次满足触发字所设定的8位序列时,才产生触发信号。同时,为了操作的灵活性,还加入了屏蔽位。若对某一位的数据不敏感,可以将其对应的屏蔽位设置为0,在判断触发条件时不对该位进行检测。