对于边缘处理器而言,架构优化是增加防御能力而不损害处理器的进程控制主要职责的关键。 为构建系统单芯片(SoC)、多芯片模块(MCM)或模拟微控制器,要做出许多决定。是保护数据链路安全还是保护处理器安全?两者都完成相同的任务,但对系统产生不同的影响。

数据链路安全性需要软件开销,并且通常会影响数据速度和联接服务质量(QoS)。典型的安全协议使用加密,这会增加处理器资源的负担。增加的资源需求与执行简单任务的远程传感器的需求不一致。数据安全加密需要频繁更新,并且可能会因为传感器脱机获取更新补丁而影响工厂输出。

保护处理器的安全是另一种方法,有机会随着系统的发展和威胁的增加而扩展。对于多处理器SoC或MCM,只需增加很少的成本,就可以添加协处理器来执行联接和安全功能。这种方法隔离了过程控制处理器(应用程序处理器),同时协处理器提供安全性并管理联接。随着人工智能(AI)变体在神经网络领域的出现,可以在协处理器上使用小型神经网络(NN),提供安全屏障阻止不受欢迎的入侵者。小型NN可以充当远程哨兵,并针对不同的威胁级别以不同的方式呈现,是一种数字伪装。它还可定期更新,同时不损害过程控制器,因此可以保持过程控制限制和标准。为了优化电源管理,可以在不使用哨兵/通信处理器时将其置于深度睡眠模式,以便应用程序处理器可以自由运行。

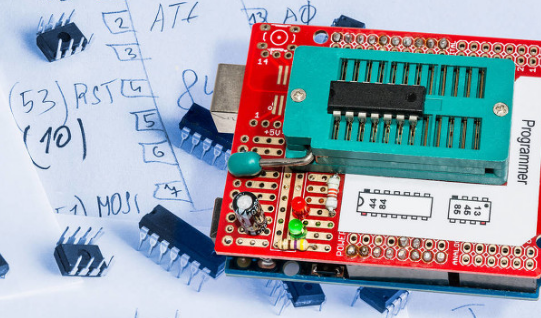

当前的封装技术为部署灵活的MCM提供了多种选择,内置安全性及哨兵/通信处理器,采用模拟接口保持传感器的精度,采用应用处理器保持工厂运转。 可以将其视为具有模拟和安全性+ MCU的节点。MCM采用最佳技术用于边缘处理器节点中的每个作业,并可从标准产品中装配。