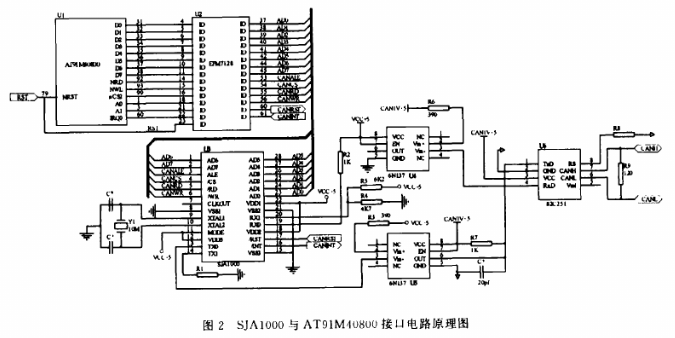

硬件接口电路设计

EPM7128用来完成接口间信号的转换与配置,EPM7128的输入来自AT91M40800的片选信号NCS2,数据线D0~D7,地址A0~A1,读信号NRD,写信号NWE和系统复位信号RST,经过内部的逻辑综合处理,产生SJA1000所需的功能信号。根据各芯片信号线的要求及端口地址的分配,可以写出CAN总线收发器的输入/输出逻辑关系表达式如下:

CAN=NCS2·A0

CANALE=NCS2•A0•(NRD+NWE)

CANRD=NRD

CANWR=NWE

CANRST=NCS2+RST

选定SJA1000的地址端口为400000H,数据端口的地址为400001H和复位端口地址为400002H。由于CAN控制器SJA1000的地址数据是复用的,通过ALE信号下降沿可以锁存总线上的地址信号。但是AT91M40800的地址总线和数据总线是单独提供的,不能直接与SJA1000的地址数据总线相连。所以要解决SJA1000与AT91M40800的接口问题,关键在于如何将访问SJA1000所需的信号送入其中。这里采用的办法是分两次I/O操作完成,第一次往地址端口400000H送入地址值作为SJA1000的单元地址。此时,片选没有选通,数据锁存在AD0~AD7总线上。第二次访问数据端口400001H时,SJA1000被选中,在ALE信号作用下将第一次的地址值写入SJA1000,CPU对SJA1000进行读/写操作。复位可以分为系统复位和程序复位两种。系统复位信号RST和程序复位信号在EPM7128中进行逻辑或操作,两者之一有效均可使SJA1000可靠的复位。

为了保证数据通信的可靠性,在CAN总线终端各连接一个120Ω的终端反射电阻,进行总线阻抗匹配。SJA1000的TX1引脚通过10k8的电阻接地,RX1引脚电平必须维持在0.5Vcc以上。否则,不能形成CAN总线所需的逻辑电平。如果通信距离较近,环境干扰较小,可以不采用光电隔离电路6N137,这时,可以将82C251的VREF直接与RX1引脚相连,从而简化了电路。