当试图将讯号从FPGA中引出以便让逻辑分析仪监视其波形时,问题就出现了。对于大规模嵌入式系统设计来说,在大多数情况下即使只有很小的修改(例如将所需要的讯号引到组件外部接脚),也可能需要很长时间才能完成FPGA的重新合成和实体建置。此外,还可能会由于不同的布局和布线而带来时序问题。执行实体建置工具所需要的实际时间依赖于电路的规模以及主计算机的性能,但很可能一天内只够完成几次除错。

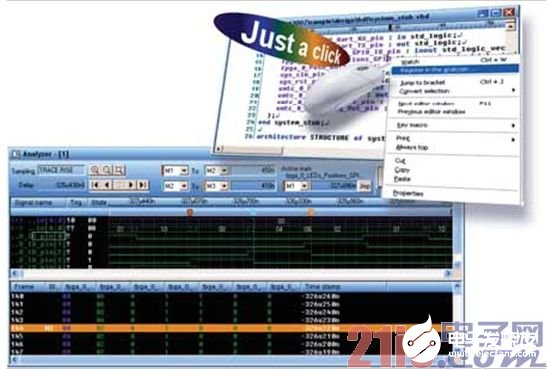

幸运的是,Computex F-sight提供了一项非常有用的功能,它不需要重新执行合成和实体实现工具就能透过设计修改把内部FPGA讯号引到组件外部接脚。这一功能被称为‘探测’(Probing)。只需在显示HDL原始程序代码的视图中简单地选择内部FPGA讯号(图2),F-Sight将自动完成其余工作,并根据上述选择为测试接脚分配合适的布线资源。这是透过利用Xilinx ISE软件工具中包含的FPGA编辑器实现的。有了这一功能,除错时必须花在逻辑合成和布局布在线的时间被缩到了最短,因而可以有更多时间用在监视讯号波形上。

图2:F-Sight探测。

协同除错

当系统工作不正常时,唯一能做的就是根据实际产生的事件检查问题产生的原因。在有些情况下,利用硬件来实现事件追踪会更容易;而在其它情况下,利用软件可能更容易一些。例如,在使用硬件的情况中,如果能够确定显示例外的讯号,那么可以将这个讯号设为触发讯号。在使用软件的情况中,如果例外处理被调用,那么可以在例外处理程序处设置断点并执行用户程序。这样事件产生的过程将被撷取进F-Sight的追踪缓冲器中。