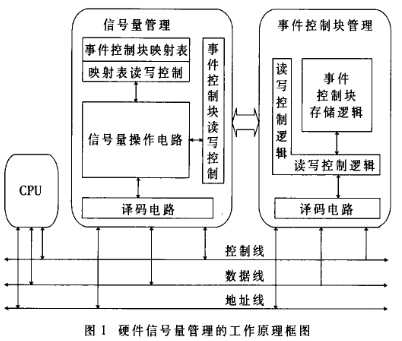

信号量管理的工作原理框图如图1所示。信号量管理模块以及事件控制块管理都是独立于CPU的逻辑结构,都可以直接从数据总线上获得数据信息进行处理,在信号量管理模块与ECB的存储模块间建立一条数据通路,在不增加总线负担的情况下加快二者间的通信。这些硬件逻辑独立于CPU工作,减少了CPU的工作,从而提高系统的响应能力。

2、 信号量管理的硬件设计与实现

2.1 ECB的设计与实现

ECB是实现信号量管理的基本数据结构,因此在设计实现信号量管理之前,要先完成ECB管理的设计与实现。本系统中ECB的结构参照μC/OS-II中ECB的结构设计。每个ECB存储单元包含一个EventType(事件类型),用于标记当前ECB被分配给信号量、互斥型信号量、邮箱还是消息队列;当一个ECB被分配给信号量时,Cnt做为信号量的计数器;ECB中的等待表lut用于存储等待当前信号量任务的优先级(μC/OS-II中没有两个任务有相同的优先级)。

ECB中等待表硬件实现的结构示意图如图2所示。等待表的结构类似一个8行8列的矩阵,存储单元编号从00~77。当一个任务在申请当前信号量而没有获得时,应将当前任务设置为等待状态,令Wr有效,以申请该信号量任务的优先级为地址,进行译码,选通相应单元后再进行写1操作。例如,申请该信号量的任务优先级Sid为111111时,对其进行译码,高三位行地址译码为10000000,低三位列地址译码为10000000,选中77单元向其写入1,则优先级为111111的任务进入等待状态。若要将一个处于等待表中的任务删除,令De有效,同样,根据地址线选通某一存储单元,向单元内写0,从而删除某一处于等待状态的任务。在控制电路中设置EventGrp 8位寄存器,用于记录当前各行中是否有等待任务;如图2所示,第i行中某一位置为1,EventGrp(i)=1,图中状态EventGrp(7)=1、EventGrp(6)=1、EventGrp(0)=0。Rd有效时,控制电路根据EventGrp采用一定算法生成优先级的高三位;根据EventGrp读出某行后生成优先级低三位;下一时钟送出最高优先级。以上为对等待表进行基本读写操作的过程。