op_alu[4:0]:ALU操作控制信号,控制ALU执行相应的算术逻辑运算。

delay:延迟控制信号,尽管采用了设置专用路径,避免了大部分的因数据相关带来的延迟,但是当指令的源操作数是前一条指令是load读存储器指令或乘法指令的结果时,需要延迟一个周期,以解决写后读的数据相关性问题。

bj[1:0]:分支跳转信号,控制地址选择器选择跳转地址。

alua[1:0],alub[1:0]:ALU操作数选择控制信号,ALU源操作数一般来自寄存器或立即数,但当采用设置专用路径技术后,还有可能来自于与该指令相关的前两条指令当前的运行结果。最后一些使能控制信号,如寄存器写使能、数据存储器读写使能等。

执行阶段主要完成指令的逻辑运算工作,ALU根据操作控制码对所提供的操作数进行相应的操作。读/写储存阶段主要完成存储器中数据的读取和写入,是微处理器系统中比较复杂的功能,在这主要完成微处理器内部数据存储器的读写。写回阶段是流水线的最后一个阶段,它将运行结果写回目的寄存器中。

5、 综合与仿真结果

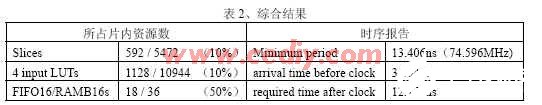

本设计采用ISE的开发环境,各个功能模块均分别在XST和ISE Simulator进行了逻辑综合和功能仿真。选择目标器件为4vfx12ff668-10,顶层模块综合结果如表2。

从综合结果可以看出,该处理器占FPGA芯片可编程逻辑单元不超过10%,最大工作频率达到74.59MHz,达到了设计要求。

使用ISE自带的仿真工器进行功能仿真,测试程序如下:

1: 20010001; //addi $1,$0,1; 6:14430003; //bne $2,$3,3;

2: 00201024; //and $2,$1,$0; 7: 24240000; //subi $4,$1,0;

3: 8C020002; //lw $2,2; 8: 00231024; //and $2,$1,$3;

4: 00221827; //rotr $1,$3,2; 9: 00412822; //sub $5,$2,$1;

5: 00030881; //xor $3,$1,$2; 10:08000005; //jump 5;

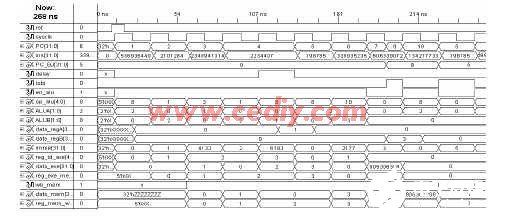

通过对波形的分析,如图4,该处理器达到了设计目的,各条指令能够正确执行,当发生数据相关时,ALU通过专用路线能够获得正确的操作数,或者发生延时。当遇到分支跳转指令时,取指逻辑能够猜测下一条指令地址,并指令译码后判断猜测是否正确。

图4、仿真测试波形

6 、结论

流水线处理器的设计关键是流水线各阶段的设计和因流水线引起的各种相关性问题的解决。本文通过对RISC处理器各关键部件进行分析,合理安排流水线。在流水线设计中,通过对因流水线引起的相关性问题进行分析研究,采用旁路技术来解决数据相关性的写后读问题,采用硬件猜测法预取分支跳转指令的目标指令,以减少流水线断流提高处理器处理速度,从综合和仿真的结果可以看到设计达到了预期的目标。本设计使用Verilog进行硬件描述设计,具有较好的可读性和可移植性,可以根据需要进行功能的增减,与其他IP核集合成SoC系统。