c)D:支持片内调试,该内核包含用于调试的硬件结构,可使CPU进入调试模块,可以方便地进行断点观察点设置、单步调试和多步调试。

d)M:采用增强型乘法器。AARM7TDMI指令集包含2个32位×32位的乘法指令和2个乘法累加MAC指令,该结构使得指令的执行比其他类型的ARM7内核减小了许多机器周期。

e)I:内含嵌入式ICE宏单元,ARM架构的处理器芯片都嵌入了Embedded ICE-RT逻辑块,便于通过JTAG接口来仿真调试RAM架构芯片。

2、芯片内部结构及特点

美国ADI公司利用其在模拟电路领域的优势,综合基于8052-8位ADμC8xx的技术积累,将ARM7TDMI内核和ADC(A/D转换器),DAC(D/A转换器)等外围设备集成在一块芯片上,就是最近推向市场的拳头产品ADμC702x系列。其中ADμC7020、ADμC7021、ADμC7022、ADμC7026等芯片除了在片上Flash和SRAM容量大小、ADC和DAC通道数量、PWM(脉宽调制)相位数量有差别外,其他完全一致;而ADμC7026,ADμC7027具有外部扩展内存接口。

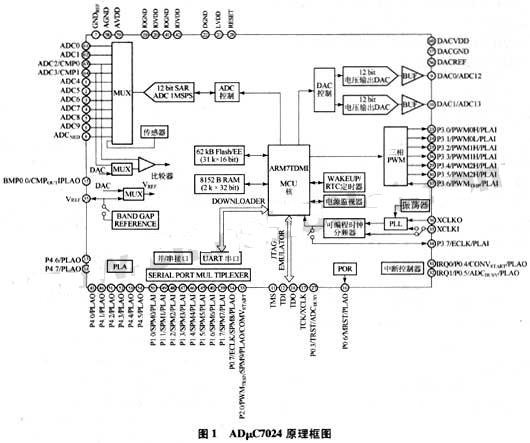

本文主要介绍其中具有代表性的一款--ADμC7024,工业级的ADμC7024工作于2.7V-3.6V电源电压,64引脚CSP封装的芯片面积仅为9mm×9mm,在1MHz时钟频率下芯片最高功耗为5mA,在最大时钟频率45MHz下芯片最高功耗为60mA。其原理框图如图1所示。

2.1 片上集成高性能的ADC和DAC

ADμC7024片上集成了10通道12位逐次逼近型ADC,能够在电源电压为2.7V-3.6V的范围正常工作,在系统时钟频率为45MHz下的最高采样率高达1MSPS(百万次采样每秒)。该ADC模块提供一个高精度、低漂移的片上2.5V基准电压VREF,该电压通过片上REFCON寄存器的软件配置也能作为输出,向外提供基准参考源。ADC能够工作于单端转换模式或者差分转换模式,在单端转换模式下的输入电压范围是0至VREF,在差分转换模式下输入电压范围是0至AVDD(AVDD通常情况下为3.3V)ADC单个或连续的转换能够被外部引脚CONVstar、片上PLA、定时器1或定时器2所触发。

通过ADC控制寄存器ADCCON,通道选择寄存器ADCCP和ADCCN软件配置好ADC后,转换结果将存储在寄存器ADCDAT位27至位16中,通过ADC状态寄存器ADCSTA的位0可以查看ADC转换是否完成,当ADC转换结束时,位0被置位;当读取ADC-DAT时,该位自动被清空。当ADC正在执行转换操作时,片上引脚ADCBusy保持高电平,一旦转换结束,该引脚马上变为低电平。

还可以通过ADCRST寄存器将ADC模块中所有寄存器恢复至默认值;通过调整ADCOF和ADCGN寄存器的值可以调整ADC转换精度,不过,该寄存器出厂时已经过校准。