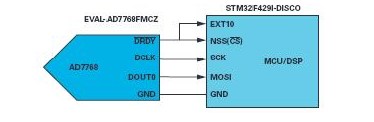

例如,使用32F429IDISCOVERY和AD7768评估板。变通SPI线的连接如图5所示。在这种设置下,AD7768的所有八通道数据仅通过DOUT0输出。

图5.AD7768通过DOUT0将数据输出到STM32F429 MCU SPI连接

需要解决的问题:

uAD7768用作SPI主机,故必须将STM32F429I SPI配置为SPI从机。

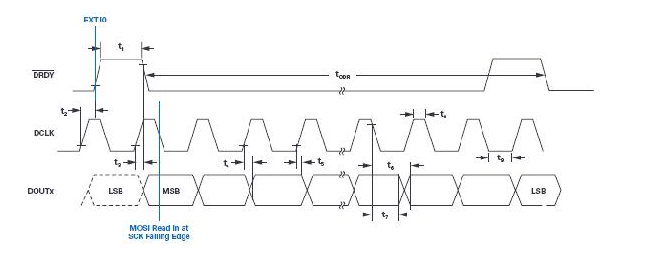

uDRDY) 高电平脉冲只持续一个DCLK周期,这不是典型的CS)。

u完成所有通道数据位的输出之后,DCLK继续输出,DRDY)为低电平。

解决方案1:MCU SPI作为从机,通过一条DOUT线与SPI主机ADC接口

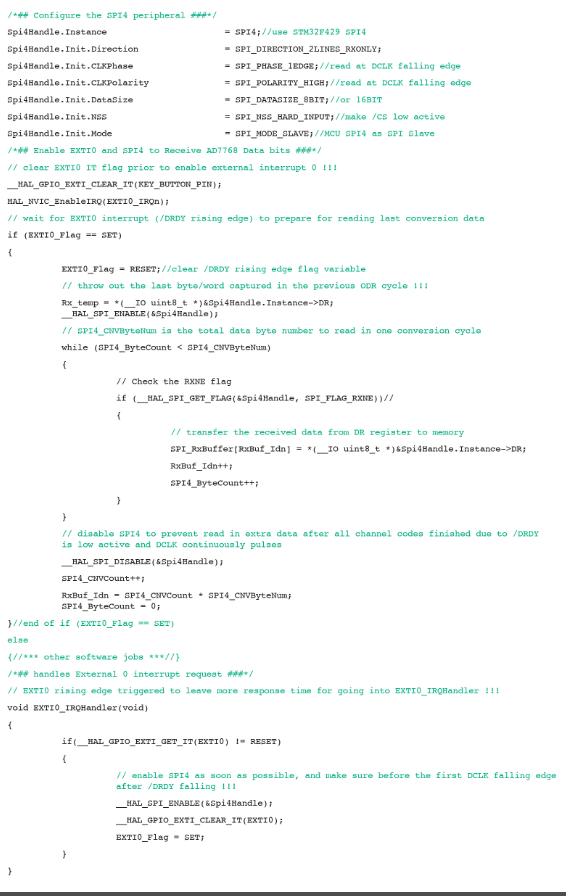

u将STM32F429的一个SPI端口(如SPI4)配置为从机,以DCLK速率接收MOSI上的数据位。

u将AD7768 DRDY)连接到STM32F429外部中断输入引脚EXTI0和NSS (SPI CS))引脚。 DRDY)的上升沿将触发EXTI0处理例程,以使SPI从机能够在DRDY)变为低电平之后的第一个DCLK下降沿开始接收数据位。时序设计在这里至关重要。

u接收到通道0至通道7的所有数据后,应禁用SPI以防止读取额外的无效数据,因为DRDY)会使SPI从机CS)变为低电平,并且DCLK保持切换。

图6.时序解决方案中的AD7768数据位读取

MCU固件开发注意事项

当软件处于中断模式时,DCLK运行速率可以高达4 MHz,实现8 kSPS的ODR。软件应进入中断处理程序,在一个半DCLK周期(375 ns)内启动SPI。为使软件更轻松地进入中断例程,MCU可以在DCLK上升沿读取数据,从而提供额外的半个DCLK周期时间。但是,t5 DCLK上升到DOUTx无效最小值为–3 ns(IOVDD = 1.8 V时为–4 ns),因此DOUTx上的传播延迟(》|t5| + MCU保持时间)应通过PCB布线或缓冲增加。

图7.配置SPI4外设

解决方案2:MCU SPI作为从机,通过两条DOUT线与SPI主机ADC接口

在第一种解决方案中,仅使用DOUT0来输出所有8通道数据。因此,数据读取将ADC吞吐速率限制为8 kSPS。如图1所示,在DOUT0上输出通道0至通道3,在DOUT1上输出通道4至通道7,可以减少数据传输时间。串行线的连接如图7所示。通过这种改进,在DCLK为4 MHz时,ODR可以轻松达到16 kSPS。