2.3 支持PCI Express总线的接口芯片

设计信号处理板卡时,为了简化板卡,提高硬件的灵活性,这里用FPGA来控制整个板卡,包括对DSP的控制、数据交换模块的设计以及接口的实现。事实上,在SAR处理中还经常用FPGA作方位向的预滤波、距离压缩等工作,所以要选用资源丰富的,速度较快的,RAM容量较大的FPGA。Altera公司推出的Stratix II GX系列完全可以胜任上述工作,其内嵌的RAM可以作为本级FIFO使用,使设计更紧凑、灵活,此外还可以对其编程实现PCI Express与局部端的通信。综合考虑,FPGA采用Altera公司的EP2SGX60E芯片。

Stratix II GX FPGA收发器工作速率为622 Mb/s~6.375 Gb/s。经过优化,FPGA能提供优异的信号完整性,降低了布板风险。在Stratix II GX器件中,收发器模块含有特定的硬件知识产权(IP),支持多种主要协议,包括PCI Express等,还可提供低功耗解决方案,特别适合散热困难的背板应用。设计中采用这个芯片,在很大程度上简化了板卡结构,提高了板卡的灵活性。

3、实时成像系统方案设计

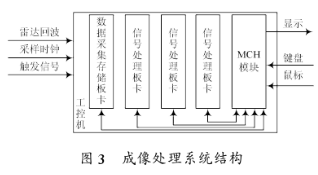

这里所设计的实时雷达成像处理系统由标准机箱、采集/存储板卡以及信号处理板卡组成。标准机箱是板卡的支撑平台并进行图像的显示。采集/存储板卡高度集成,实现雷达回波的实时采样和实时存储。基于4片ADSP-TS201的信号处理板卡是成像处理的核心,4片DSP采用并行、流水的方式以达到实时成像处理的要求。采用PCIExpress总线能够有效地利用PC机资源和应用软件,利于开发图形化操作界面,极大地方便了信号处理系统的调试、状态监控以及图像显示。AD采样的数据一边存入FLASH阵列,一边传给DSP进行实时处理,处理完的结果通过PCI Express总线读入计算机内存并进行显示。信号处理板卡是专门为雷达成像设计的一种通用处理模块。4片DSP峰值并行处理可达到12 GFLOPS的运算(DSP内核工作在500 MHz)。实际中根据算法的复杂度选取信号处理板卡的数量。成像处理系统结构如图3所示,其中MCH模块用来控制板间通信。

3.1数据的采集与存储

采集/存储板卡设计时将采集和存储集成在一块板卡上,可以设计成高速和低速两种采集/存储卡。高速卡适合于对高速的中频采样,如直接对高分辨SAR雷达中频回波采样;低速卡适合于精度要求高、速度要求低一点的场合,如在ISAR的Dechirp后以及普通的SAR基带回波采样。采样后的数据经FPGA控制存人FLASH阵列。板卡上有128 GB容量的FLASH阵列,通过72片FLASH芯片并行操作(其中64片FLASH用来存储数据,8片FLASH用来提供冗余校验,这样即使有几个芯片损坏也可以保证数据的完整性),可以实现240 MB的稳定连续读写速度,可应用于高速大容量存储的场合。板卡采用标准PCI Express接口,主机可以直接读取采样数据并进行显示。