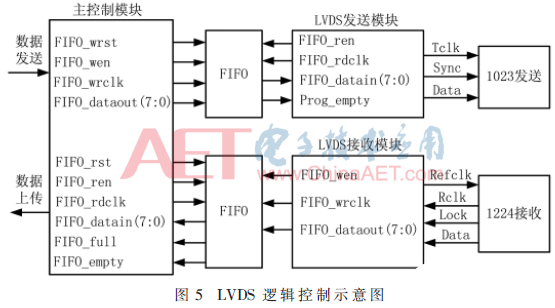

LVDS接收模块在时钟Rclk的上升沿,对从被测设备接收到的数据进行纠错;在时钟Rclk的下降沿,判断若接收到的数据为有效数,则内部的数据有效信号置1,将有效数据发送给FIFO,通过主控制模块上传至CPCI总线。

4 CPCI总线接口实现

目前,CPCI总线接口的实现主要有2种方法:(1)使用可编程逻辑器件自行设计;(2)使用专用的协议转换芯片,将CPCI总线转换为用户自定义的本地总线[8]。第二种傻瓜式的实现方法虽然不如第一种方法灵活,但胜在省时省力,简单易用,开发周期短,因此应用较为广泛。

4.1 PCI9054工作模式

本设计采用PLX公司的PCI9054协议转换芯片,其本地工作模式采用逻辑控制简单、开发难度较低的C模式,该模式下PCI9054芯片内部的地址线和数据线相互独立,用户可以自行定义需要的本地时序,实现CPCI接口的通信功能。CPCI接口与本地总线之间的数据传输有3种方式:PCI Initiator模式、PCI Target和DMA模式。PCI Target模式是CPCI主设备通过PCI9054发起对本地总线上资源的访问;DMA模式即PCI9054通过控制CPCI和本地两条总线来实现数据的突发传输。本设计主要工作是命令字的下发和数据的上传,考虑操作的简易度,对于命令字的下发采用Target模式下的单周期访问模式,对于数据的上传采用DMA模式突发传输[9]。

PCI9054与CPCI总线的连接是通过CPCI连接器J1实现的,即PCI9054的CPCI信号通过串接10 Ω匹配电阻与J1的相应信号引脚连接,串接10 Ω电阻是为了减少总线分支因为较大的背板阻抗对总线产生的瞬态干扰,保证信号传输的准确性。PCI9054的本地时钟由外部有源晶振提供,且与FPGA端的时钟同步。在FPGA内部划分一块FIFO作为数据缓存,利用其双口操作的特性实现数据的跨时钟域传输,同时也方便了本地时序的设计。

4.2 CPCI本地总线接口实现

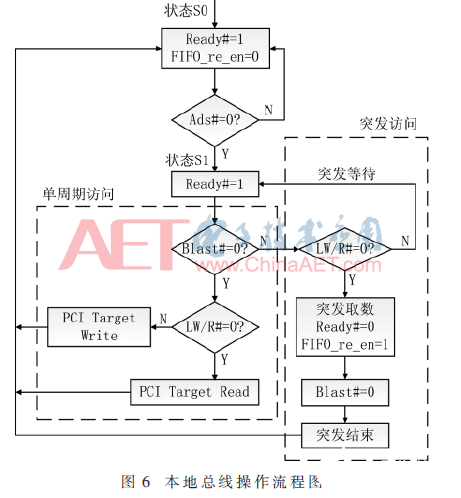

CPCI本地总线接口是本设计的核心所在。整个CPCI接口的设计思路是:主控芯片FPGA通过桥接PCI9054与CPCI总线交互,由其内部逻辑自定义本地总线的工作时序实现对总线的状态控制,同时产生片内读写及地址信号完成单周期读写和突发传输的功能。在FPGA内部划分一块FIFO作为数据缓存来实现数据突发读取,由其半满信号作为上位机的读取标志。基于这种设计思路,为了保证通信的可靠性,本文设计了类似握手协议的通信方式,具体操作如图6所示。