在整个USB3.0链路的布局布线设计中,应考虑下列因素:(1)所有PCB线路和互连电缆均采用完全阻抗匹配的90欧姆差分设计。(2)必须最大限度地减少非差分耦合线路。(2)非差分耦合线路会严重影响眼图的内眼张开程度。(3)90欧姆差分耦合PCB线路的线路宽度和线路间隔不应太窄,以避免造成额外的损耗,同时便于生产。从生产的角度而言,差分线路的理想线路宽度为0.3毫米,线路间隔为0.2毫米,这会形成200微米的电介质高度(假设FR4,且er=4)。(4)差分耦合链路的正电和负电线路(包括USB3.0电缆)之间的延迟(线路长度)完全相同(最大限度地减少斜率下降)。对于保持很高的信号完整性和避免生成共模信号,这一点很重要。

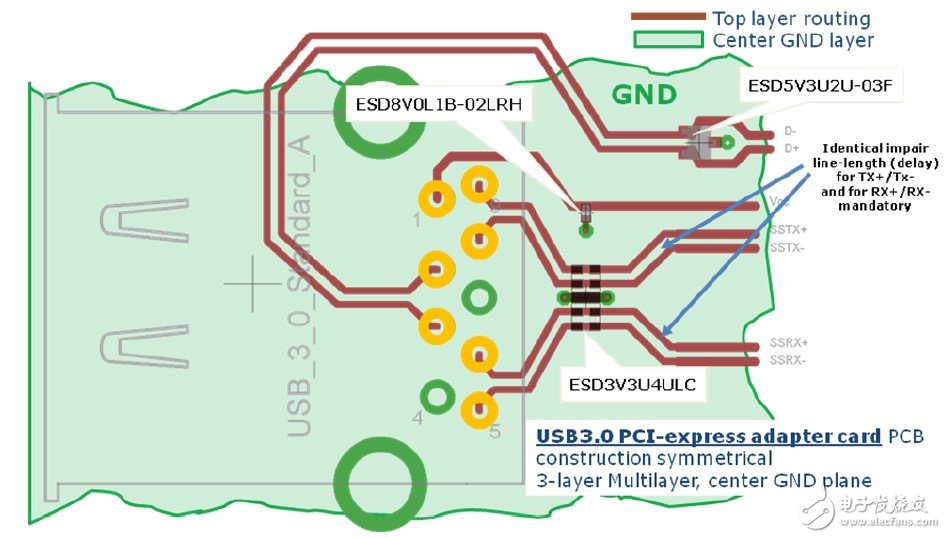

图5为具备ESD防护电路的USB3.0标准A连接器横截面的布局布线设计示例。

图 5:具备ESD防护电路的标准A连接器USB3.0布局布线设计建议。

USB3.0的新型ESD防护策略

持续不断地减小芯片的各个组件的尺寸是降低生产成本、提高工作频率的根本,但与此同时,这种微型化也产生了新的问题(如容易发生ESD击穿)。因此,对提供可靠的ESD防护机制的要求与日俱增。

USB3.0可提供最高5Gbps的数据率,因此基本频率高达2.5GHz。为实现很高的信号完整性,数据信号的上升时间和下降时间必须非常短。对第3谐波或第5谐波的处理,不应发生明显衰减。这些只能通过利用寄生效应最小、半导体开关速度最快的尖端半导体制程才能实现。这种微型化半导体结构的缺点,是对ESD冲击造成的过压的耐受能力降低。采用内置ESD防护装置,会引起寄生效应(寄生电容),并且需要占用很大的片上空间。

一种十分经济高效的方法,是同时采用内置ESD防护机制(集成到USB3.0收发器中),以及专为提供外部ESD防护而定制的性能增强(即高电流)应用电路(由器件/电路设计者在电路板上实现)。内置ESD防护机制旨在提供器件级保护,例如,严格遵守HBM JEDEC JESD 22-A115要求。内置ESD防护对在开发、生产和电路板装配过程中安全地拿放器件很重要。专为该应用定制的外部TVS二极管则按照IEC61000-4-2标准,实现了更加严格的系统级保护。

为提供适当的USB3.0系统级ESD防护,ESD防护器件(TVS二极管)必须满足不同的要求。可参照IEC61000-4-2标准,根据残留箝位电压和TVS二极管对ESD冲击的响应,判断TVS二极管的ESD防护性能。

TVS二极管的ESD防护性能会受TVS二极管的一些特性影响,比如最低R_on(动态电阻R_dynamic)和专为该应用定制的最低V_breakdown。