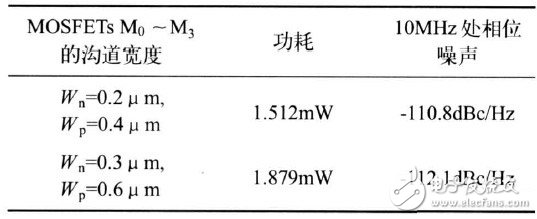

表2 器件尺寸不同时测得的功耗及相位噪声

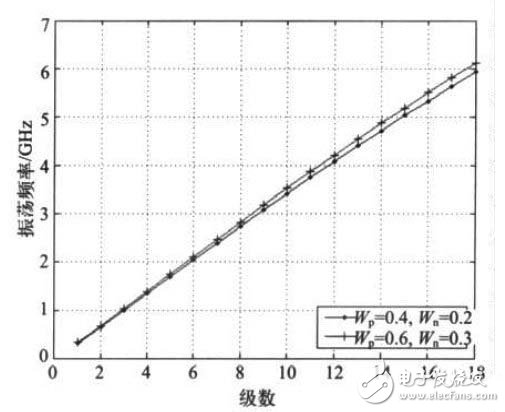

图7 器件尺寸不同时测得的频率调节范围对比

4 结论

该数控振荡器结构采用全静态CMOS逻辑电路来设计,获得了线性度较好的频率调节范围,在90nm混合信号工艺条件下全DCO电路功耗在3mV左右,10MHz处相位噪声低于-110 dBc/Hz,性能相比传统LC压控振荡器有过之而无不及,非常适合应用于高性能数字电路中。在用该数控振荡器结构设计DPLL 时,应进一步增加环形振荡器级数以提供线性度更好的可调输出频率范围,并需要前置数字环形滤波器提供相配合的控制信号。

责任编辑;zl

关于接口,总线,驱动就介绍完了,您有什么想法可以联系小编。