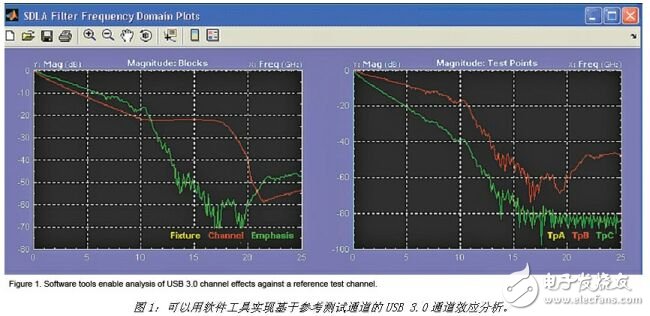

评估USB 3.0串行数据链路的另外一个重要部分是测量波形和互连通道行为之间的复杂交互。以下假设已经不再成立:因为发送端输出信号符合眼图模板,所以在所有通道达到给定损耗条件下设计都能正常工作。为了理解在给定最差通道条件下发送端的余量,除了一致性要求外,你还需要建模通道和电缆的组合,并使用通道建模软件分析通道效应(图1)。

发送端的一致性测试

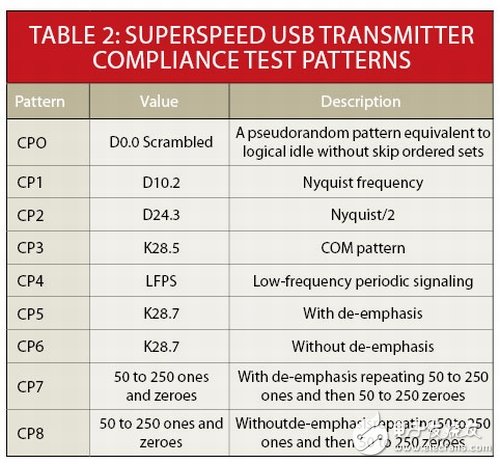

发送端测试需要使用各种测试图案(表2)。每种图案的选择依据是与评估图案的测试有关的特征。CP0是一个D0.0扰码序列,用于测量确定性抖动(Dj),比如数据关联抖动(DDJ)。而CP1是一种无扰码的D10.2全速时钟图案,不产生DDJ,因此更加适合用于评估随机抖动(RJ)。

抖动和眼图高度是在应用均衡器函数和合适的时钟恢复设置(二阶锁相环或PLL,闭环带宽是10MHz,阻尼系数为0.707)之后用100万个连续单位间隔测量的。抖动结果的计算方法是以1 x 10-12的误码率(BER)从测量数据总量中提取抖动性能。例如,利用抖动外推法,目标RJ等于测量得到的RJ(rms)乘以14.069。

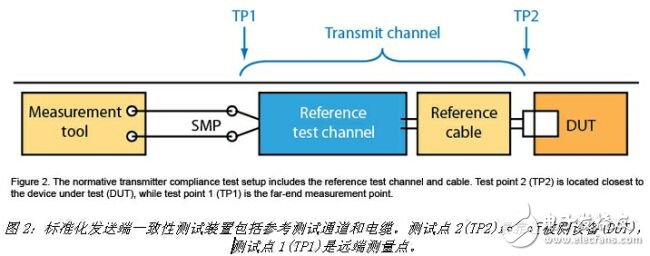

图2显示了标准化的发送端一致性测试装置,其中包括参考测试通道和电缆。测试点2(TP2)最靠近被测设备(DUT),而测试点1(TP1)是远端测量点。所有发送端的常规化测量都是在TP点的信号上进行的。

在TP1点采集到信号后,可以使用一款称为SigTest的软件工具进行数据处理,类似于正式的PCI Express一致性测试。对于要求预先一致性测试、表征或调试的应用,还可以用其它工具深入观察不同条件或参数下的设计行为。带USB 3.0特定软件的高速示波器可以提供自动的标准化和信息化PHY发送端测试。这些工具可以确保测试设备得到了正确配置,从而有效节省时间。

在测试完成后,一份详细的通过/失败测试报告将突出显示可能存在设计问题的地方。如果在不同测试位置(例如公司实验室,测试室)之间出现矛盾,应该使用前次测试运行时保存的数据再次执行测试。

在要求进一步分析的场合,可以用抖动分析和眼图分析软件进行查错和设计表征。例如,一次可以显示多个眼图,允许工程师分析不同的时钟恢复技术或分析软件通道模型的效果。另外,可以使用不同的滤波器分析SSC效应,最终解决系统互操作性问题。