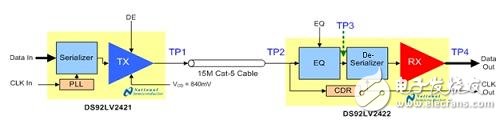

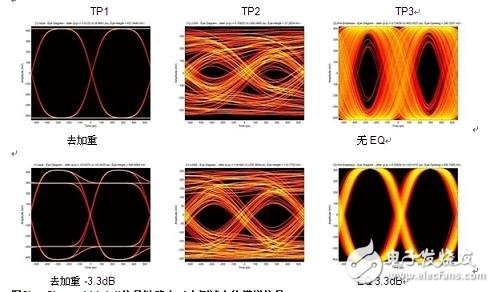

如图2a所示,美国国家半导体新一代的Channel Link II SerDes,在串行器DS92LV2421的发送阶段即有去加重功能;而在解串器DS92LV2422的接收阶段则有电缆均衡功能。框图下所示(图2b)的是当运行数据率为1.8Gbps,在信号路径上的三个测试点的模拟信号。左侧图片所示的是在去加重关闭的情况下,TP1处的波形,此时设定为-3.3dB。为了补偿预计在传输介质上会出现的高频损耗,在发送端进行了去加重补偿。在Channel Link II器件中,去加重和EQ都由寄存器控制,有8个设定值。如TP3处的数据所示,使用去加重和EQ可产生显著的效果。在VOD=840mV(在TP1处的差分输出电压)时,无去加重或EQ信号,在TP3的幅度是290mV,抖动是403pS。而当信号DE=-3.3dB,EQ=3.3dB时,幅度是825mV,抖动是142pS。

图2a:国半SerDes Channel Link II框图

图2b:Channel Link II信号链路上三个测试点的模拟信号

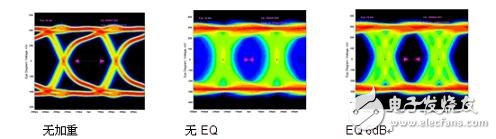

图3是数据从TP1到TP3的示波器截图,使用的是10米的CAT-6 STP线缆,运行数据负载为1.8Gbps。测试数据点位于解串器的输入端,不附加EQ。可以看到均衡器在接收数据时变化明显,当EQ设定为0dB,眼图完全封闭;而当EQ是6dB时,眼图完全打开。时钟和数据恢复(CDR)电路是恢复数据的关键,在解串器内CDR电路紧随EQ阶段后。CDR电路的设计目的在于恢复数据,避免字节错误,其眼图呈50%或0.5UI(典型)闭合态。

图3:数据从TP1到TP3的示波器截图

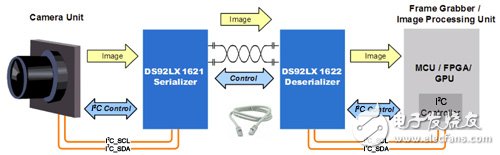

Channel Link III器件DS92LX1621和DS92LX1622是SerDes的最新产品,解决了以往的所有问题。图4显示的串行器可以直接连接到16位LVCMOS并行总线摄像头,该摄像头可在单向交流耦合CML通道上串行数据。其中,摄像头的时钟和双向I2C控制线也可编码到串行数据中。串行数据、时钟和I2C总线通过带有分立时钟的16位并行总线实现解串,经I2C接口到帧接收器或FPGA的接收端。解串器无需额外的外部时钟,这既降低了成本,也降低了设计难度。此外,解串器与串行器自动同步功能使其实现了真正的“即插即锁”功能。

图4:基于Channel Link III SerDes的应用实例一