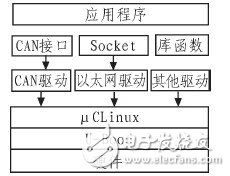

图3 软件结构

2 硬件设计

2.1 LPC2294最小系统

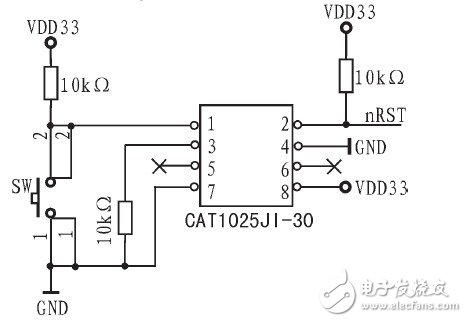

LPC2294采用LQFP144封装,最小系统需要模拟和数字3.3 V电源以及核心电源1.8 V.为了便于串口波特率的设置,外部接11.0 592 MHz晶振。P2.26(BOOT0)通过10 kΩ电阻上拉,P2.27(BOOT1)接一跳线座,通过跳线让P2.27可选择接高电平或低电平以选择从内部FLASH或外部NORFLASH启动。由CAT1025构成手动复位监控电路,提高了系统的可靠性。当SW按键按下时,CAT1025的2引脚输出持续为大于150 ms的低电平,LPC2294复位。在CAT1025的2引脚通过10 kΩ电阻上拉,防止产生错误的引脚输出状态,复位电路如图4所示。

图4 复位电路图

2.2 SRAM和NORFLASH电路

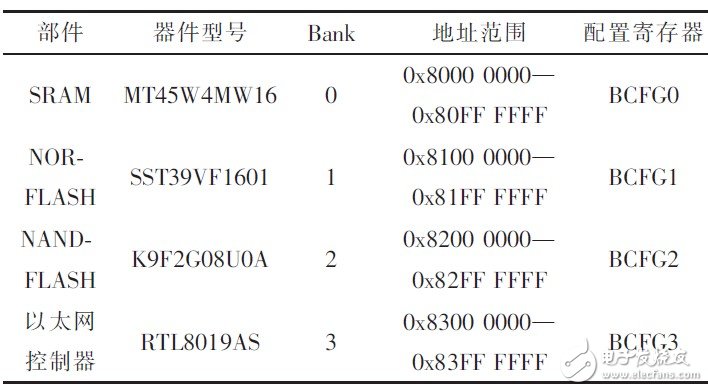

为了运行μCLinux操作系统,必须扩展系统RAM与FLASH.LPC2294具有外部存储器控制器(EMC),该部件可同时支持多达4个单独配置的存储器组。每个存储器组都支持SRAM、ROM、Flash EPROM、Burst ROM以及外部I/O设备。主节点外部存储器地址分配情况如表1.

表1 主节点外部存储器地址分配情况

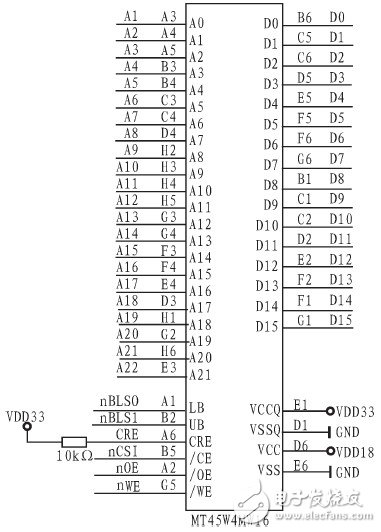

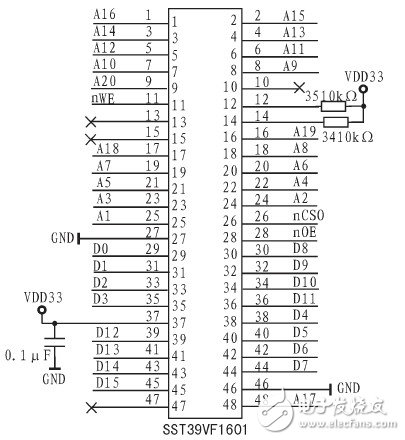

主节点采用的SRAM和NORFLASH分别是MT45W4MW16、SST39VF1601.MT45W4MW16是一个16位、8 MB容量的PSRAM.SST39VF1601是一个16位的CMOS多功能Flash MPF器件,储存容量为2 MB.其电路连接如图5、图6所示。

图5 SRAM电路连接图

图6 NORFLASH电路连接图

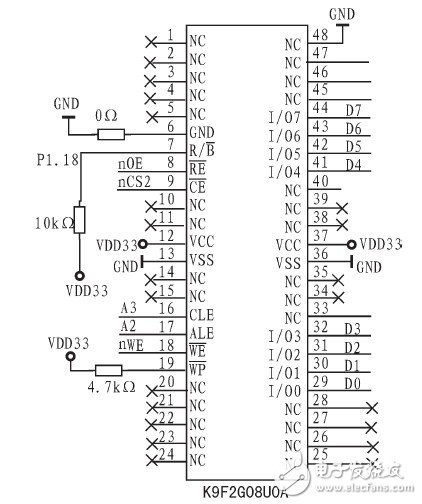

2.3 NANDFLASH电路

NANDFLASH用作存放μCLinux的根文件系统和应用程序,使用Jff2文件系统格式。NANDFLASH采用三星公司的K9F2G08UOA,存储容量为256 M.NANDFLASH的数据接口为8位串行接口,使用nCS2作为片选线,地址区间使用0x8200 0000-0x82FF FFFF,CLE(指令使能)和ALE(地址使能)分别连接到地址总线A2和A3,因此NANDFLASH的数据写入地址为0x82000000,命令写入地址为0x82000004,地址写入地址为0x82000008.R/B(准备/忙等待)连接到P1.18,用于读取当前状态,此引脚须上拉。其电路连接如图7所示。