1. 硬件设计

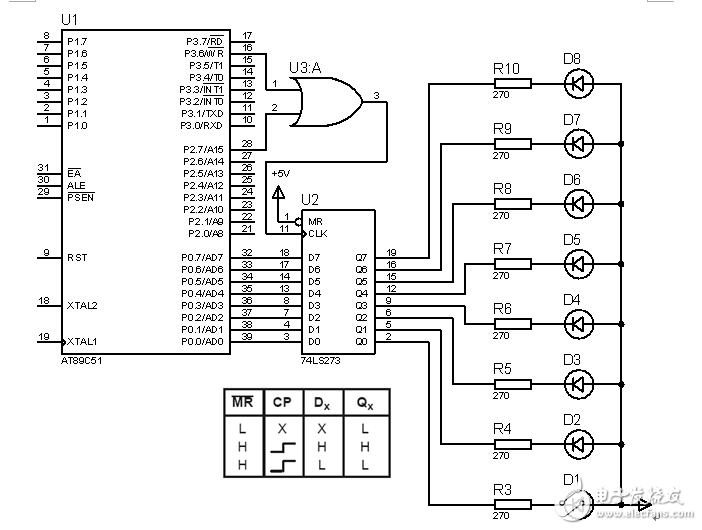

创建一个新的Design,添加如下元件(略去晶振和复位电路):

元 件 名所 在 类参 数备 注

AT89C51Microprocessor ICs

8051 Family

LED-YELLOWOptoelectronics

Leds

LED

RESResistors

Generic270Ω电阻

74LS273TTL 74LS Series

Flip-Flop & Latches双稳态多谐振荡器&闭锁锁存器

74LS32TTL 74LS Series

Gates & Inverters门电路 & 反相器或门

用8个发光二极管显示单片机的输出数据,输出为低电平时LED灯亮。74LS273的D0~D7为8位数据输入端,接单片机的P0口,Q0~Q7为8位数据输出端,CLK为触发时钟输入端,MR为数据清除使能端。采用或门74LS32进行地址译码,U3:A的输入端分别接单片机的P2.7口和WR口,输出端接74LS273的CLK口。

从74LS273的真值表可以看出,当MR为低电平时,所有的Q端为0,否则Q端随D端而定,因此,MR应置为高电平。CLK在上升沿时完成数据锁存操作,因此U3:A的输出必须完成一个由低到高的变化。当写指令有效时,输出低电平,只有P2.7同时为低电平时,才能在写指令完成时实现一个由低到高的电平变化,这样在写完成后,数据被74LS273锁定。可见,74LS273地址应该为0XXX XXXX XXXX XXXX,一般我们设为7FFF。

2. 程序设计

在Keil C51中,有以下的内存类型:

code 以 MOVC a,@A+DPTR 读取的程序内存

data 可以直接存取的内部数据存储器

idata 以 Mov @Rn 存取的内部数据存储器

bdata 可以位寻址(Bit Addressable)的内部存储器

xdata 以 MOVX @DPTR 存取的外部数据存储器

pdata 以 MOVX @Rn 存取的外部数据存储器

为了定义使用方便,在absacc.h文件中对此进行了宏定义,比如此例中的地址0x7fff,就可写为XBYTE[0x7fff]。

#include “at89x51.h”

#include “absacc.h”

#define A74273 XBYTE[0x7fff]

void main(void)

{

A74273 = 0x2b;

while(1);

}

注意了:当写指令有效时(应该是WR,无效时为高),输出低电平,只有P2.7同时为低电平时,才能在写指令完成时实现一个由低到高的电平变化,这样在写完成后,数据被74LS273锁定。可见,74LS273地址应该为0XXX XXXX XXXX XXXX,一般我们设为7FFF。

关于接口,总线,驱动就介绍完了,您有什么想法可以联系小编。