在整个系统中,FPGA根据DSP对各个通道是单端或者差分的设置,以及各个通道使能与否和采用率分频值的设置,控制ADS8517以及多路选择器,将A/D输入的数据以及其对应的通道存入一个FIFO中,当FIFO半满时向DSP发送中断,由DSP读取FIFO中A/D的采样数据及其对应的通道号。可以看出,设计重点主要集中在多路选择器的设计以及FPGA中硬件逻辑的设计。

2.1 多路选择模块设计

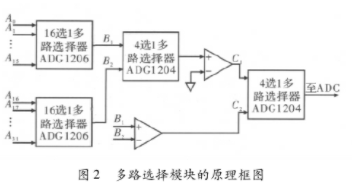

根据系统要实现的功能,多路选择模块的设计采用如图2所示的设计思路,其中16选1多路器和4选1多路器分别采用ADI公司的ADG1206和ADG1204。由FPGA控制这些多路选择器来选择通道以及单端/差分模式,在设计选择差分信号时,为方便,只支持A0~A15通道和A16~A31通道依次对应的差分,而不支持A0~A15通道中任意一个通道和A16~A31通道中任意一个通道的差分。

2.2 FPGA部分的设计

由于DSP数据总线为32位双向总线,所以在FPGA中需要设计一个总线的三态控制器,来控制总线的输入输出,这部分设计较简单,模式相对固定,应用已成熟。

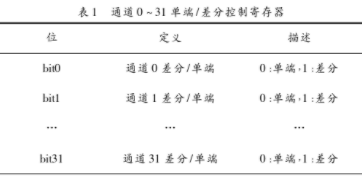

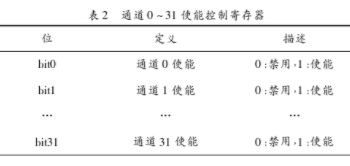

对于DSP发出的各个通道单端/差分控制,各个通道使能控制以及采样率分频值设置这些控制信息,由在FPGA中开辟出的3个32位寄存器来存储。通道单端/差分控制寄存器和通道使能寄存器的定义如表1和表2所示,采样率分频值设置寄存器中的32位无符号2进制整数表示相应的分频值。

当DSP的控制信息设置好以后,根据通道单端/差分控制寄存器以及通道使能控制寄存器中的内容,建立一个使能通道索引表,索引表中字的个数等于使能的通道数,每一个字的字长为6位,依次将使能的通道号转换成二进制无符号数后放入表中各个字的低5位,每个字的高位记录相应的通道是单端还是差分,‘0’表示单端,‘1’表示差分。

设计采用ADS8517并行输出的工作模式,按照图3所示的并行输出方式时序图对其进行控制,其中

和BYTE信号为ADS8517的输入控制信号,的下降沿表示一次采样的开始,为高电平时表示可以读取A/D的输出数据,输出为并行8位输出,当BYTE信号为低电平时输出高8位,反之则输出低8位,从而完成16位分辨率的输出。为ADS8517输出信号,为低电平时则表示本次A/D转换正在进行,为高电平时表示本次转换完成,因此当和同时为高电平时,便可以读取本次A/D采样转换后的数据。