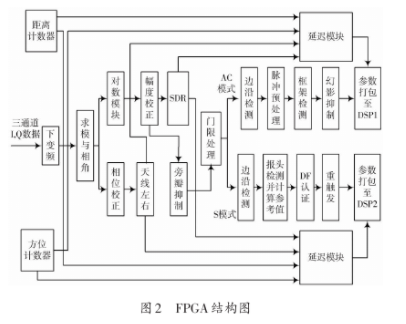

FPGA完成三通道采样、下变频、AC码、S码检测提取,两片DSP 分别完成AC 码、S 码点迹处理。FPGA 同时完成与航迹管理机双向通信,及控制发射机的发射时序。

系统接口一般有FIFO和双口RAM,前者适于顺序事务处理,但速度慢,而且需要加同步头,不适于DMA处理。这里全部采用FPGA内部的双口RAM,并且置为乒乓结构,这样可利用DMA 高速处理大量数据。同时为了加快处理速度,DSP外总线全部采用同步方式。

根据性能要求,为了同时装配4路AC码,专门设计了接口同时捕获4路信号,并顺序处理捕获的信号。

2 系统软件流程及功能

从系统的性能及硬件结构可以看出,FPGA的任务相当复杂,要完成解码、发射及相应的通信功能。解码框图如图2所示,基本过程是下变频,幅度、相位校正,门限处理,再分别AC通道和S通道处理。

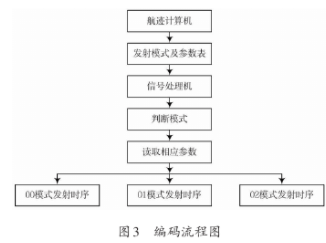

FPGA除了完成解码、还要完成编码和时序控制功能,编码框图如3所示。由于航迹管理机有空中飞机的历史航迹,因此发射模式是由航迹管理机来配置的。航迹管理机根据历史航迹来确定某一方位的询问是全呼叫还是点名,并确定回答概率等参数。然后并将这些参数传入发射模式表。编解码根据方位读取相应参数,并产生相应编码脉冲。

2.1 编码主要系统软件流程及功能

2.1.1 下变频模块

二次雷达要求和、差、控制三通道同步,因此系统中频放到了信号处理机,这样便于同步。系统中频是60 MHz,采样80 MHz,采样后,必须滤波并抽取。下变频一般用DDS模块,但DDS占用资源较大,这里I,Q通道各自只用了4个预置值。一般预置值I通道采用[1,0,-1,0],Q通道采用[0,1,0,-1]。但这样遇到采样值是[1,0,-1,0]或[0,1,0,-1]时,一个通道输出是0.因此这里采用[ 2 2, - 2 2, - 2 2, 2 2],[ 2 2,2 2, - 2 2, - 2 2],这样保证每一个通道都有输出值。但这样做会扩大了数据位数,直接截位会影响小信号检测。为了不影响小信号处理,必须在抽取滤波时加大数据位数,最后再截位处理。

2.1.2 求模与相角

求模与相角采用cordic核,这样将I,Q数据转化为模与相角。表1 是cordic 核数据范围表,输入的I,Q的范围是[-1,1]。在cordic 核中模与相角分别采用1QN、2QN 表示形式,例如在幅度是用1QN 表示的。假设cordic 核的数据长度是10 位,即幅度用1Q8 表示中,因此1和-1表示为: