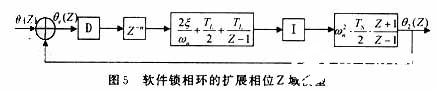

其中:D表示数据抽取,I表示数据内插。数据在抽取之前先要进行抗混叠滤波,可用于抗混叠滤波的FIR滤波器有CIC滤波器、半带滤波器等。

实际情形中,由于零阶保持内插几乎不需要额外的运算量,因此经常被采用。实际上环路频率fL总是能够跟上环路滤波器输出信号的变化速率。换言之,对环路滤波器输出信号按照fL的速率进行采样保留了他的全部信息,因此零阶保持内插对系统性能不会有太大影响。

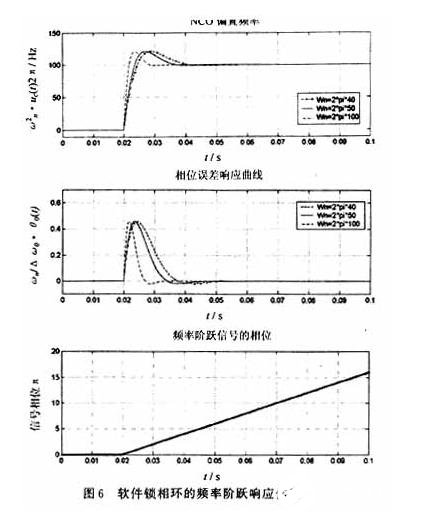

结合上述软件锁相环的基本原理,下面借助Matlab仿真观察软件锁相环的系统响应。本文以频率阶跃信号作为输入,观察软件锁相环的系统响应从而进一步验证本文建立的一系列软件锁相环模型。

设定系统采样频率为1 MHz,仿真时间0.1 s,信号中心频率125 kHz,起始相位-π/4,输入频率阶跃100 Hz,起始点为0.02 s,抽取因子为8。一般情况下,都希望环路工作在欠阻尼状态,取阻尼因子ξ=0.707,ωn由2π ΔF(快捕带宽)决定,分别取2π*40,2π*50,2π*100。仿真出相位误差响应曲线、NCO偏置频率曲线和频率阶跃信号的相位曲线,如图6所示。

从图6可以看出,软件锁相环在[0,0.02]区间内相位误差为0,处于锁定状态。在t=0.02 s时刻,输入信号频率产生了大小为100 Hz的阶跃,导致软件锁相环进入捕获过程。由于软件锁相环的校正作用,当ωn=2π*50时,系统在t=0.05 s时刻重又进入同步状态,相位误差依旧为0。由相位误差响应曲线可以看到,锁相环可以无相差的跟踪频率阶跃信号,同时表明虽然锁相环鉴相误差为0,但是由于环路滤波器的理想积分作用其输出的控制信号并不为0,由该控制信号产生的100 Hz偏置频率保证了NCO输出与输入信号的同步。当快捕带宽发生变化导致改变时,锁相环的捕获速度也发生了变化,快捕带宽越宽,捕获速度越快。

4 软件锁相环的DSP实现

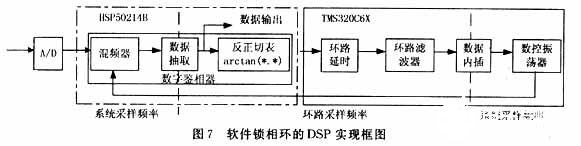

在宽带数字化接收机的实现中,数字下变频采用通用可编程下变频器HSP50214B。在实现载波同步、码元同步软件锁相环的整个反馈环路中,数控振荡器、鉴相器由HSP50214B完成,环路滤波在TMS320C6X中完成。DSP实现框图如图7所示。

环路延时是一个应该重视的因素。带来软件锁相环环路延时主要有以下2种原因: