3D NAND利用垂直整合极大地增加了存储设备的存储密度。以往,结构局限于两个维度,通过减小尺寸从而限制密度;如今,结构在第三个维度中得以扩展。这些设备包括非常规几何图形以及极高的深宽比特征,这带来了独有的工艺挑战。

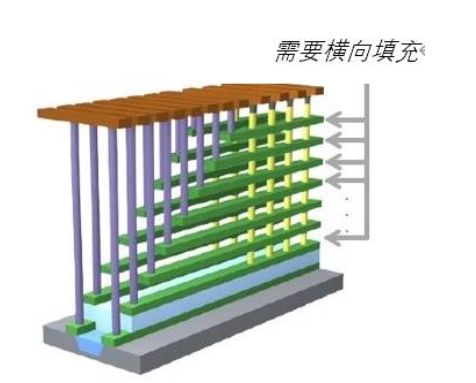

其中最具挑战性的是向字线中填充导电钨。3D NAND交替堆叠氧化物和氮化物介电层,当前一代中有多达96层,更高层数还在研发中(图 6)。密集排列且具有高深宽比的孔渗透至这些层中,按照高深宽比通道将排列分为字线。为了创建存储单元,必须移除氮化物层并以钨进行替换。这种钨必须通过深(垂直深度 50:1)通道引入,然后横向扩散,从而以无空洞的超共形沉积方式填充(之前的)氮化物水平面(横向比约 10:1)。原子层沉积能够一次沉积一个薄层,这就确保了均匀填充,并防止因堵塞而产生的空隙。

一种成功的方法就是在填充工艺中添加形状选择性抑制剂,防止在填充较高深宽比结构之前,出现较低深宽比结构中的过度沉积。由内而外的ALD工艺可以完全填充横向(水平)线且不留空隙,同时最大限度地减少了垂直通道中的沉积,从而提升了电气性能和工艺成品率。

图 6. 3D NAND采用复杂的高深宽比结构。创建字线需要超共形钨沉积,而这必须填充垂直和水平空间且不留空隙。

结语

原子层刻蚀与沉积工艺利用自限性反应,提供原子级的控制。工艺产量提升、从更小的结构中移除的材料减少、以及对原子级控制的需求不断增长,这些因素都重新引起了人们对原子层刻蚀的兴趣。原子层工艺提供的控制水平,确保其在当前乃至未来的半导体制造业中将发挥越来越重要的作用。

关于工艺,制造就介绍完了,您有什么想法可以联系小编。