(1)先进工艺节点:“晶圆厂+Fabless+EDA”协同推进的成果

首先,SOI、FinFET等新器件结构的发明将带来晶体管电学和物理特性的变革;其次,在半导体工艺制造方面,摩尔定律的演进伴随着众多不可预知的物理问题逐渐浮现。处于摩尔定律推进一线的晶圆厂从材料、化学、工艺过程控制等各种制造细节来创新、调试和求证。而EDA公司借助晶圆厂积累的大量测试数据探索物理效应和工艺实施细节的准确和高精度模型化。然而,这并不意味着新工艺节点研发的终点,顶尖Fabless公司将基于此模型和工具进行芯片设计与试产,并且依托强大和丰富的芯片设计不断发现和排除新工艺节点在模型和制造中的各种量产问题。在此期间,芯片设计工程师、EDA公司的AE、晶圆厂工程师等等往往长年累月在一起办公,集中攻破新问题,修复新bug。晶圆厂、Fabless、EDA三者通力合作,反复迭代,如此才能最终将达到商用和量产要求的工艺节点推向市场。一旦有一个环节出题,前功尽弃。

因此,摩尔定律任何一代最先进工艺节点,无一不是由拥有最先进工艺制造条件的晶圆厂、顶尖EDA团队和设计经验丰富的Fabless公司三者协力共同推进的成果。这也是为什么台积电最先进制程的第一批产品总是由苹果、高通、华为来发布,只有顶尖的Fabless公司才具备参与调试最先进工艺节点的能力。这也是为什么三大EDA巨头始终把控细分市场的一个重要的原因。

(2)数学问题

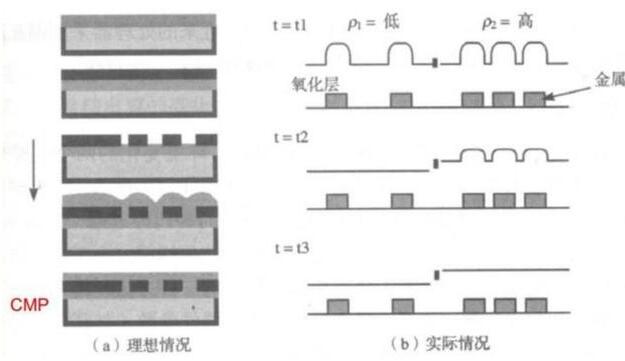

以一个铝互连时代工艺过程中经典的互连线偏差问题为例,在形成铝互连线时二氧化硅层夹在互连图形的金属层之间,氧化物淀积在已经成形的金属层上,一般都会留下一些台阶高度或者表面形貌,在理想情况下,采用CMP方法对层间电介质进行厚度剖平后如图a所示。

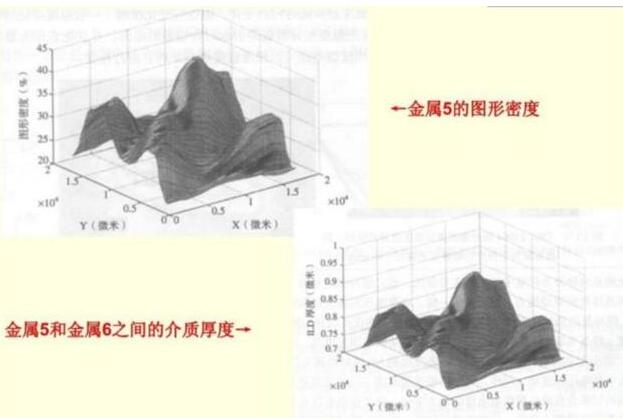

但实际的情况是,虽然在特定范围内能够达到很高的平整度,但从整个芯片范围上来讲平整度就很有限,如图所示,不同的厚度又对电介质的电容等电特性产生不同的影响。

EDA工具要做的事就是尽可能高精度地在虚拟的软件世界中重新和拟合类似上述现实中的物理和工艺问题,以期望在芯片设计阶段将其纳入考虑范围之内,以系统性的方法和预测性的裕量来应对和纠正,最终保证芯片设计仿真结果同流片结果一致。