图1:差分对线接收端的匹配电阻的布局。对接收端的匹配电阻到接收管脚的距离要尽量靠近。同时匹配电阻的精度要控制。对于点到点的拓扑,走线的阻抗通常控制在100Ω,但匹配电阻可以根据实际的情况进行调整。电阻的精确度最好是1%-2%。因为根据经验,10%的阻抗不匹配就会产生5%的反射。

三、串行LVDS信号的仿真分析

以上分析了LVDS信号设计时必须注意的事项,虽然在PCB设计的时候一般都会遵守以上的规则进行,但是为了能够提高设计的正确性和准确行必须对PCB进行信号完整行仿真,通过仿真得到信号的串扰、延时、反射和眼图波形,从而达到设计即正确的目标。信号完整性问题的仿真流程是先建立元器件的仿真模型,然后进行前仿真确定布线过程的参数和约束条件,物理实现阶段按照约束条件进行设计,最后进行后仿真,验证设计是否满足设计要求。在整个流程中模型的精确性直接影响仿真的结果,而在前仿真和后仿真阶段用到的仿真分析方法对于仿真结果同样至关重要,而在本设计中采用了精确度较高的spice模型。下面结合实际的项目来说明仿真在本设计的实施过程。

3.1.PCB叠层设置

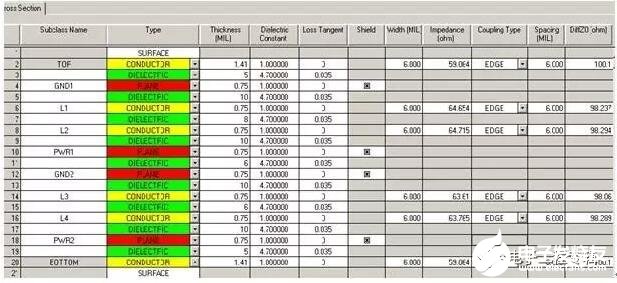

由上面的分析知道,PCB板的叠层设置和信号的耦合以及阻抗计算都有着密切的关系,所以在开始PCB设计之前必须进行叠层设计,然后进行信号的阻抗计算。在本设计中的叠层设计见下图:

图2:叠层设计由于PCB密度较高,本设计采用10层板的叠层结构,经过合理的安排叠层厚度,通过allegro计算,表面微带和内层带状线的差分线在线宽6㏕线间距6㏕时,阻抗理论计算值分别为100.1和98.8Ω。符合阻抗控制要求。

3.2.设置直流电压值

这一步骤主要是为某些特定的网络(一般是电源地等)指定其直流电压值,确定DC电压加在网络上,执行EMI仿真需要确定一个或多个电压源管脚,这些电压值包涵了模型在仿真过程中使用的参考电压信息。

3.3.器件设置

在allegro仿真的时候allegro会把器件分成三大类:IC、连接器和分立器件(电阻电容等),allegro会依据器件类型来给器件的管脚分配仿真属性,分立器件和连接器的管脚属性为UPSPEC,而IC的管脚属性可以为IN、OUT和BI等。

3.4.模型分配