3)设计检查。MAX+plus Ⅱ为设计者提供完善的检查方法设计仿真和定时分析。其目的是检验电路的逻辑功能是否正确,同时测试目标器件在最差情况下的时延。这一查错过程对于检验组合逻辑电路的竞争冒险和时序逻辑电路的时序、时延等至关重要。

4)器件编程。当电路设计、校验之后,MAX+plus Ⅱ的Programmer将编译器所生成的编译文件下载到具体的CPLD器件中,即实现目标器件的物理编程。

文本输入方式和图形输入方式设计一个模60计数器

系统分析

模60计数器是可由一个10进制计数器和一个异步清零6进制计数器组成的。本设计采用10进制计数器74160组件和6进制计数器组成。数字系统分块后,需要选择正确描述系统逻辑功能的方式。对于所选用的CPLD,需要用相应的设计开发软件。如MAX+plus Ⅱ的设计描述方式有文本、波形、图形多种方式。图形输入方式直观易懂。当系统较大时,由于此方式连线多,使用十分不方便。采用VHDL硬件描述语言的描述方式与结构无关,设计难度降低,软件修改方便而且大部分受控功能模块已经编译验证,系统设计时只要选择这些模块并按一定的逻辑功能组合即可。

本设计6进制计数器采用文本输入方式设计,其代码如下:

LIBRARY ieee ;

USE ieee. STd_LOGIC_1164. all ;

USE ieee. std_logic_unsigned. all ;

ENTITY counter6 IS %定义模块IS

PORT (Load,En Clrn,Clk:IN STD_LOGIC;

D:IN STD_LOGIC_VECTOR(2 downto 0) ;

%定义输入端口

Q:OU T STD_LOGIC_VECTOR(2 downto 0) ;

%定义输出端口

Co:OU T STD_LOGIC)

END counter6 ;

ARCHITECTURE a OF counter6 IS

BEGIN %定义过程

PROCESS(Clk)

variable tmp:std_logic_vector (2 downto 0) ;

%定义一个矢量

begin

IF Clrn =’0’THEN tmp:= “000” ;

else

IF( Clk’event AND Clk =’1’) THEN %过程声明

IF Load =’0’THEN tmp:= D ;

ELSIF En =’1’THEN

IF tmp = “101” THEN tmp:= “000” ;

ELSE tmp:= tmp + 1 ;

END IF ;

END IF ;

END IF ;

END IF ;

Q 《 = tmp ; Co 《 = (tmp (0) AND tmp (2) AND En) ;

END PROCESS ;

END a ;

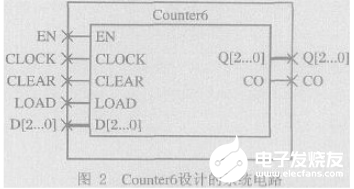

保存并编译设计代码,然后创建电路符号counter6,接着用图形输入方式编辑模60计数器,在编辑的过程当中可以引用6进制电路符号counter6。设计的系统电路如图2所示。

模60计数器由十进制计数器74160和以上设计的六进制计数器组成(见图3),当74160计到9时,产生进位使6进制电路能计数。