为了降低电源供电系统的阻抗,应遵循以下一些设计准则:

1. 降低电源和地板层之间的间距;

2. 增大平板的尺寸;

3. 提高填充介质的介电常数;

4. 采用多对电源和地板层。

然而,由于制造或一些其他的设计考虑,设计工程师还需要用一些较为灵活的有效的方法来改变电源供电系统的阻抗。为了减小阻抗并且消除那些谐振峰,在PCB上放置分立的去耦电容便成为常用的方法。

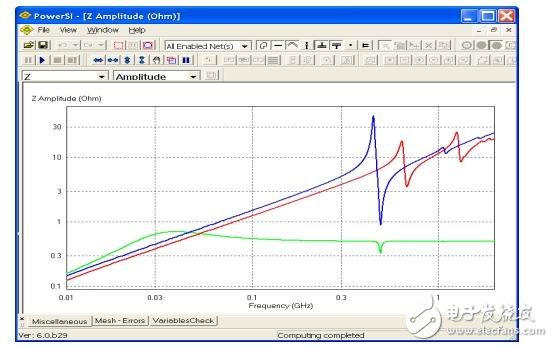

图4显示了在三种不同设置下,用Sigrity PowerSI计算得到的电源供电系统的输入阻抗:

a. 没有电源整流模块,没有去耦电容放置在板上。

b. 电源整流模块用短路来模拟,没有去耦电容放置在板上。

c. 电源整流模块用短路来模拟,去耦电容放置在板上。

从图中可见,例子a蓝线,在集成电路芯片的位置处观测到的电源供电系统的输入阻抗在低频时呈现出容性。随着频率的增加,第一个自然谐振峰出现在800MHz的频率处。此频率的波长正对应了电源地平板的尺寸。

例子b的绿线,输入阻抗在低频时呈现出感性。这正好对应了从集成电路芯片的位置到电源整流模块处的环路电感。这个环路电感和平板电容一起引入了在200MHz的谐振峰。

例子c的红线,在板上放置了一些去耦电容后,那个200MHz的谐振峰被移到了很低的频率处(《20MHz),并且谐振峰的峰值也降低了很多。第一个较强的谐振峰则出现在大约1GHz处。由此可见,通过在PCB上放置分立的去耦电容,电源供电系统在主要的工作频率范围内可以实现较低的并且是平滑的交流阻抗响应。因此,电源供电系统的噪声也会很低。

图5:针对不同结构仿真计算得到的输入阻抗。不考虑芯片和封装结构(红线);考虑封装结构(蓝线);考虑芯片、封装和电路板(绿线)。在板上放置分立的去耦电容使得设计师可以灵活地调整电源供电系统的阻抗,实现较低的电源地噪声。然而,如何选择放置位置、选用多少以及选用什么样的去耦电容仍旧是一系列的设计问题。因此,对一个特定的设计寻求最佳的去耦解决方案,并使用合适的设计软件以及进行大量的电源供电系统的仿真模拟往往是必须的。

协同设计概念

图4实际上还揭示了另一个非常重要的事实,即PCB上放置分立的去耦电容的作用频率范围仅仅能达到几百兆赫兹。频率再高,每个分立去耦电容的寄生电感以及板层和过孔的环路电感(电容至芯片)将会极大地降低去耦效果,仅仅通过PCB上放置分立的去耦电容是无法进一步降低电源供电系统的输入阻抗的。从几百兆赫兹到更高的频率范围,封装结构的电源供电系统的板间电容,以及封装结构上放置的分立去耦电容将会开始起作用。到了GHz频率范围,芯片内电源栅格之间的电容以及芯片内的去耦电容是唯一的去耦解决方案。