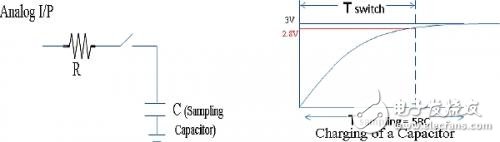

模拟输入路径的电阻决定采样所需的时间(如果C相同,采样时间将随着R的增加而增加,采样时间等于电容器的充电时间)。采样相位通过一个开关控制。在ADC IP设计的一个可编程寄存器指定的时段内,该开关保持关闭。

也就是说,任何模拟值存储到采样电容器的时间由使用可编程寄存器的ADC设计决定。我们称该时间为Tswitch。同时,模拟输入需要一定的时间给采样电容器充电,这等于电容器通过阻抗路径的采样时间(RC)。我们将这段时间称为Tsampling。对于被采样的模拟值:

Tsampling<Tswitch (等式1)

Tswitch在ADC IP内编程,而Tsampling只由集成决定。因此,作为SoC设计人员,我们需要确保实现Tsampling最小化。一种方法是使该路径的电阻保持最小。这种情况请参见图3。

图3:为采样电容器提供的充电时间不足的后果

图字:模拟I/P;C(采样电容器);电容器充电

我们在ADC转换过程中经常讨论SNR劣化。对于ADC来说唯一可以轻松避免的噪声源是由于开关关闭时间不足而引入的误差,或由于ADC阻抗路径的采样时间过高而引入的误差。基本情况下,Tsampling或Tswitch不符合上述标准。

信道分类

信道可以两种方式进行分类:第一种方法是根据信道的ENOB(有效位数)规格进行分类,即精密和非精密信道,第二种方法是根据模拟输入的来源划分,是来自于SoC外部还是内部,即外部信道和内部信道。

根据ENOB规格

精密信道是指ENOB(以及SNR)较高的信道。需要确保满足等式1才能符合较高的SNR规格。大多数SoC的设计都通过使精密信道的MUXing深度保持较低水平来实现,因为路径中的每个MUX都会引入一些R以及一些C。此外,SoC中精密信道数也有限,因为信道路径中的MUX的阶决定对模拟输入可见的有效电容(由于电荷共享,其信道的电容器的充电时间会非常高)。

因此MUX的阶必须非常小,这意味着SoC中精密信道的数量也非常少。非精密信道是指SNR规格不严格的信道。精密信道和非精密信道如图2所示。因此,SoC中的非精密信道通常较多,而ADC精密信道的数量有限。

信道可以是内部或外部信道

ADC的信道可以是外部信道(来自于padring)也可以是内部信道(SoC内其它IP的输出)。

内部信道

需要知道一个IP输出到ADC输入的路径电阻的精确估算值,才能了解ADC能够提供的最小采样时间。如果采样时间低于该值,那么采样电容器充电会不足,采样值也不正确。然后,这个不正确的值将被量化,从而导致SNR劣化。