如果时钟源有抖动,SD ADC可能会产生10-12dB的SNR劣化。但无论什么类型的ADC,时钟抖动在一定程度上都可能会影响采样。ADC工作的时钟源与系统时钟源一样,取决于SoC的工作模式。对于RC振荡器,时钟的抖动较大,因此SNR劣化较高,而对于PLL,抖动较小,因此SNR劣化也较低。因此,需要平衡时钟源导致的SoC电流消耗和ADC的转换质量。

ADC的工作参考电压

SoC中的ADC设计需要既能够在外部电源的参考电压下工作,也能够在内部参考电压下工作。ADC使用的各种参考电压都有其特定的问题。让我们逐一讨论。

外部参考电压

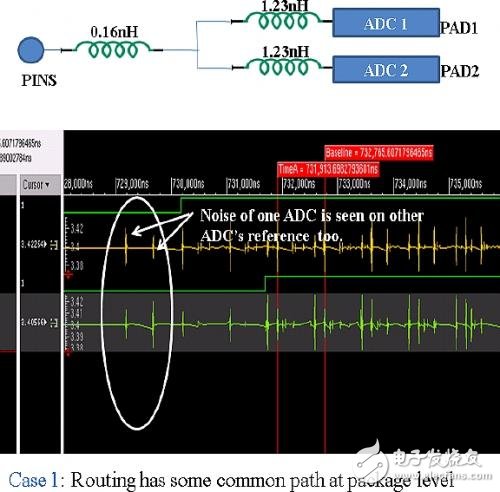

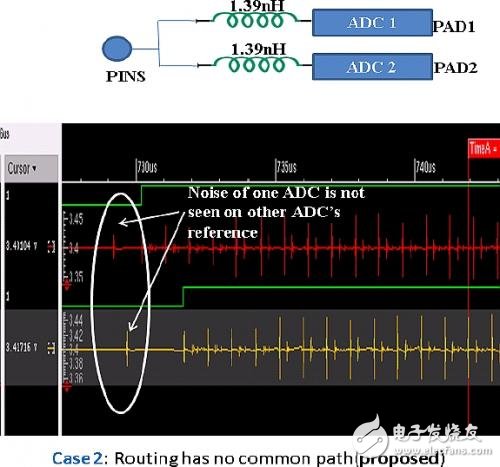

如果ADC使用的参考电压是外部电压,通常会产生与参考共享有关的问题。这是SoC的一个久而未解的问题,原因是一个非常简单的限制,那就是SoC能够拥有的粘合引脚数有限。SoC提供的外部引脚和焊盘数量有限(目的是降低成本),因此通常的做法是使SoC中的不同ADC共享参考电压。这就是由于一个ADC进行转换而导致到达另一个ADC的参考电压不稳定的原因(两个ADC之间的串扰)。这些串扰问题没有在IP层模拟中解决,导致SoC级SNR性能不佳。

避免出现这种问题的一种方法是在设计时将去耦合电容器放在IP的参考焊盘附近,这会减少参考电压的不稳定性。但这会增加芯片的尺寸,进而增加芯片的成本。因此,设计人员想出了了一个替代方案,那就是在封装上减少两个焊盘之间的公共结合线路径,并将引脚电容器放在电路板上。通常,SoC中应避免ADC参考焊盘共享。

图5:ADC的外部参考共享串扰问题

外部参考

通常来说,内部参考电压是一个带隙参考电压,它是SoC内产生的绝对参考电压。应确保在ADC开始转换之前,该电压值已经稳定下来。如果情况并非如此,那么转换量化相位将出现错误。通常对该问题的推荐变通方案是,SoC中的电源管理单元应向ADC发送指示,告知带隙参考电压已获得了稳定值,ADC可以开始转换流程。

图6:ADC开始转换之前应获得内部参考稳定指示

本文小结

SNR劣化现已成为ADC设计人员的专业术语。SoC本身存在许多集成问题,导致SNR劣化。本文重点介绍了一些常见问题以及可行的解决方案。设计人员需要确保集成正确无误。