上述讨论提出了另外一个问题,即如何有效地将PLL杂散成分限制在一定的范围内,使其不对发射频谱产生影响。一旦发现了杂散成分,首先想到的方案就是将PLL环路滤波器的带宽变窄,以便衰减杂散信号的幅度。这种方法在极少数的情况下是有效的,但它存在一些潜在问题。

图5给出了一种假设的情况,假设设计中采用了一个具有20MHz相对频率的N分频合成器,如果环路滤波器是二阶的,截止频率为200kHz,滚降速率通常为40dB/decade,在20MHz频点可以获得80dB的衰减。如果参考杂散成分为-40dBc(假设可以导致有害的调制分量的电平),产生杂散的机制可能超出环路滤波器的作用范围(如果它是在滤波器之前产生的,其幅度可能非常大)。压缩环路滤波器的带宽将不会改善杂散特性,反而提高了PLL锁相时间,对系统产生明显的负面影响。

经验证明,抑制PLL杂散最有效的途径应该是合理的接地、电源布局和去耦技术,本文讨论的布线原则是减小PLL杂散分量的良好设计开端。考虑到电荷泵中存在较大的电流变化,采用星型拓扑非常必要。如果没有足够的隔离,电流脉冲产生的噪声会耦合到VCO的电源,对VCO频率进行调制,通常称为“VCO牵引”。通过电源线间的物理间隔和每个Vcc引脚的去耦电容、合理放置接地过孔、引入一个串联的铁氧体元件(作为最后一个手段)等措施可以提高隔离度。上述措施并不需要全部用在每个设计中,适当采用每种方式都会有效降低杂散幅度。

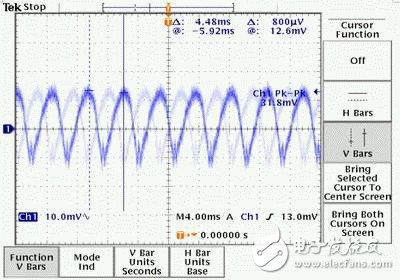

图6提供了一个由于不合理的VCO电源去耦方案所产生的结果,电源纹波表明正是电荷泵的开关效应导致电源线上的强干扰。值得庆幸的是,这种强干扰可以通过增加旁路电容得到有效抑制。另外,如果电源布线不合理,例如VCO的电源引线恰好位于电荷泵电源的下面,可以在VCO电源上观察到同样的噪声,所产生的杂散信号足以影响到ACPR特性,即使加强去耦,测试结果也不会得到改善。这种情况下,需要考察一下PCB布线,重新布置VCO的电源引线,将有效改善杂散特性,达到规范所要求的指标。

图6:不合理的VCC_VCO去耦测试结果

关于EDA,IC设计就介绍完了,您有什么想法可以联系小编。