2 常规电路

通过上述分析,我们知道带隙基准由两个部分组成,一部分是晶体管的偏置,另一部分是与绝对温度成比例的电压(Proportional to the Absolute Temperature,PTAT)。正负温度系数电压刚好相互抵消。衡量带隙基准电压性能一般采用两个参数,温度系数(Temperature Coefficient,TC)和电源电压抑制比(Power Supply Rejection Ratio,PSRR)。

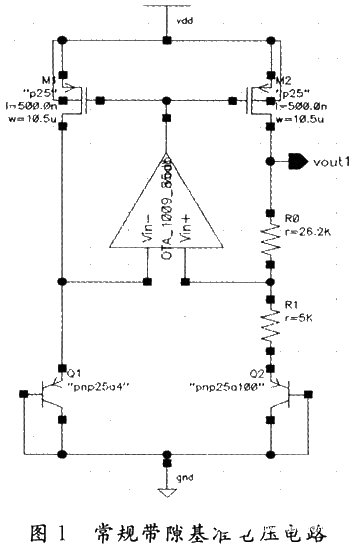

图1所示为常规带隙基准电压电路。

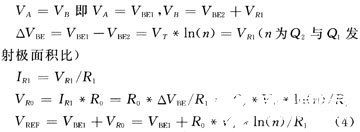

设运放Vin-和Vin+相应的节点为A和B,根据理想运放输入两端虚断的特点:

式(4)就是由常规电路得到的带隙基准电压VREF。在2.5 V工作电压,进行-25~125℃温度扫描,从扫描结果(图4中Voutl)可以看到,该电路得到的VREF大概在1.2 V左右,温度系数TC=5.65 ppm/℃。对电源电压进行2~3 V扫描,VREF从1.18 V变化到1.179 V,电源电压抑制比PSRR=55.4 dBo该电路的温度系数还不够理想,而且VREF不可调节,因此在常规电路的基础上进行改进。

3 改进电路

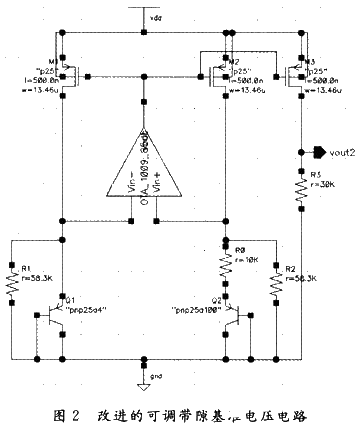

由于常规电路的温度系数还不够理想,而且VREF不可调节,因此改进常规电路。图2是文献提到的改进电路。

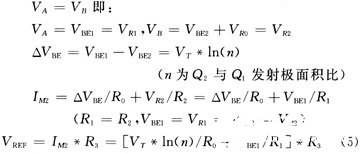

分析该电路,同样设运放Vin-和Vin+相应的节点为A和B,根据理想运放输入两端虚断的特点:

式(5)就是改进电路得到的带隙基准电压VREF。设R。=10 kΩ,通过VREF/ T=0,n=25,T=300 K时 VBE/T△-1.5 mV/℃和 VT/ T△+0.087 mV/℃,可以计算出R1和R2的近似值。在2.5 V工作电压,进行-25~125℃温度扫描,从扫描结果(图4中Vout2),可以计算出改进电路的温度系数TC=5.37 ppm/℃。对电源电压进行2~3 V扫描,VREF从62l.2 mV变化到620.5 mV,电源电压抑制比PSRR=52.9 dB。VREF可以通过改变R2的阻值进行调节,可调节范围约为O~2.25 V,实际应用中,考虑电阻在工艺上的误差,R3不宜取太小的阻值,因此VREF很难取到较小但又要求比较准确的电压,同时为了保证输出支路的PMOS管工作饱和区,所以合适的调节范围约为O.5~2 V。从计算结果发现改进电路的温度系数5.37 ppm/℃与常规电路的温度系数5.65 ppm/℃相比没有得到较大改善,因此电路还需改进。

4 曲率补偿的带隙基准电压电路