3 结 语

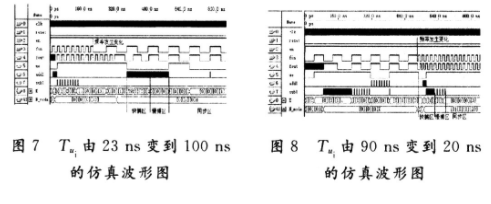

通过计算机仿真可以看出:设计的全数字锁相环具有很快的锁相速度,大量的实验表明在7个输入信号周期内环路就进入锁定状态。从图5和图6的仿真结果可以看出,设计的全数字锁相环锁频范围很宽。另外,锁相精度和系统的外部高频时钟有很大关系,如果时钟频率很高,那么锁相精度就越高。同时,外部高频时钟与该全数字锁相环的带宽也有很大的关系,在鉴频锁存模块是把外部高速时钟分频后的时钟作为时钟源的,因此,外部高频时钟频率越高,经过鉴频得到的分频值N才能越准确。总之,该设计的自动变模的全数字锁相环在外部时钟频率很高的情况下,不仅具有较快的锁相速度,而且具有较宽的锁频范围和较高的锁相精度。

该设计的全数字锁相环结构简单,易于集成,可采用VHDL语言完成系统设计,方便使用EDA软件进行综合仿真,可制成片内锁相环。下一步需要重点做的工作是:研究如何应用环形数控振荡器,使用控制字来控制环形数控振荡器的输出代替该设计中的外部高速时钟源;另一方面,在除N分频模块研究如何使用小数分频的技术提高了系统的精度。

责任编辑:gt

关于模拟技术就介绍完了,您有什么想法可以联系小编。