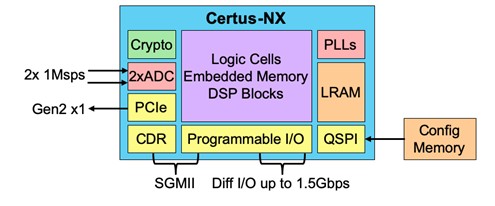

图2. Certus™-NX示意图。全新FPGA拥有实现AES和椭圆曲线加密的硬核模块、用于千兆位以太网(SGMII)的时钟和数据恢复(CDR)、PCIe Gen2控制器以及模数转换器(ADC)。

FD-SOI工艺可实现基体偏压(back-bias),与CMOS工艺相比,漏电降低75%。在1.0V电压下工作会降低有效功率。该工艺还提高了芯片的可靠性。由于FPGA将其配置存储在SRAM中,因此随机软错误可能会导致器件故障(SEU)。相比于CMOS,FD-SOI工艺能够消除SRAM超过99%的软错误,从根本上避免了SEU的发生。

Certus™-NX产品提供各种封装,其中最小尺寸仅为6x6 mm。该设计的低功耗特性减少了电源连接和接地的数量,从而为I/O留出更多空间。最小的封装尺寸有82个I/O,最大的封装(14x14 mm)则拥有192个I/O。莱迪思还缩短了将FPGA配置加载到SRAM所需的时间,从而缩短了启动时间。若使用Quad-SPI连接外部闪存,Certus™-NX-40的启动时间少于14ms。而I/O在3毫秒内即可完成初始化。

产品比较

对于需要PCIe的应用,Certus™-NX-40与市场上的另两款产品形成竞争关系,即英特尔的Cyclone V和赛灵思Artix-7系列FPGA。后两者都是具有硬核PCIe接口、采用28nm CMOS工艺的FPGA。对于这款产品,我们都选择了有50000个逻辑单元的型号作为对比,因为它们下一级较小的型号仅有33000个逻辑单元,远低于Certus™-NX。如表1所示,这两款竞品的总存储容量略大,对应的门数也较多,同时还提供更多的DSP模块。

用于PCIe设计的FPGA。Certus™-NX提供更优的加密性能,支持以太网和更快的I/O速度。*该范围对应不同封装尺寸;*该数据是针对PCIe Gen2接口,在严格测试环境下Tj =85ºC,125MHz测得的。

Certus™-NX在多方面表现出色。它支持最优的加密,提供用户模式AES加速以及FPGA配置位流的验证(ECDSA)和加密。英特尔和赛灵思的两款产品缺少验证,仅支持AES配置。尽管Cyclone FPGA的两个PCIe Gen1通道可以提供相同的总带宽,但它不提供PCIe Gen2支持,并且它不提供用于以太网设计的硬核CDR模块。Certus™-NX的I/O速度最高,其封装尺寸仅为其他产品的三分之一,可大大节省电路板面积。

对于不需要PCIe接口的应用,Certus FPGA则与Cyclone V E系列和Spartan-7系列两款产品竞争。表2对比了Certus™-NX-17与上述系列中逻辑单元数量相似型号。尽管Certus™-NX的逻辑单元略少,但它的存储空间更大,既有嵌入式存储器又有外部的大型存储器,使其能够缓冲更多数据或存储更大的神经网络。与之前一样,Certus™-NX在加密方面更为突出,I/O速度更胜一筹。其6x6 mm的极小封装尺寸所需的电路板面积不到两款竞品的四分之一,并且I/O密度约是它们的两倍。Certus™-NX也是该组产品中唯一具有以太网硬核的FPGA。