使用 IDELAY实现高效过采样

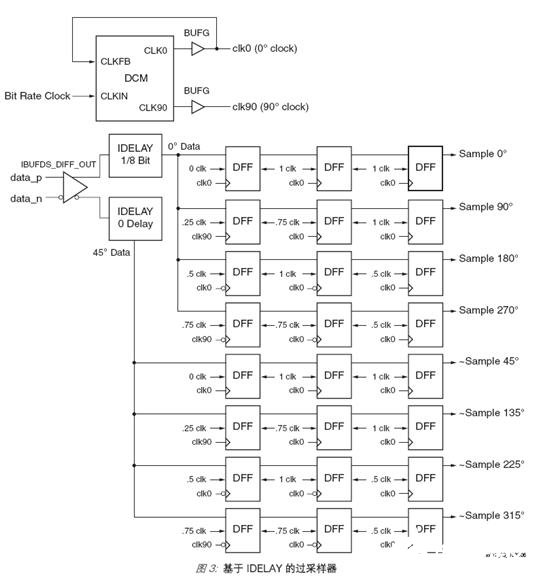

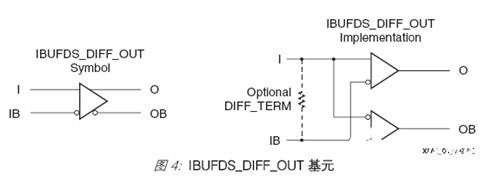

图3 所示为基于 IDELAY 的过采样器。一个 DCM 用来创建间隔 90 度的两个时钟相位。使用这两个时钟相位的两个边沿,可以在一个位周期内给定四个间隔均等的采样点。串行比特流通过称为 IBUFDS_DIFF_OUT 的基元进入 FPGA。因为此基元仅支持 LVDS 输入,所以串行数据必须为 LVDS 格式。一般的 LVDS 输入基元只向 FPGA 提供一个信号,但 IBUFDS_DIFF_OUT 基元会将接收到的真实信号及其反转信号都提供给 FPGA。如图4 所示,IBUFDS_DIFF_OUT 使用两个差分接收器,一个在 LVDS 对的 P 输入 IOB 中,另一个在其 N 输入 IOB。这些差分接收器各向 FPGA 提供一个信号,N 侧 IOB 发出的信号与 P 侧 IOB 提供的信号反相。

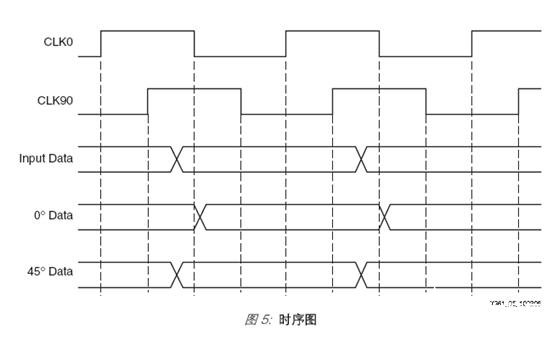

Virtex-4 和 Virtex-5 器件中的每个 IOB 都有一个 IDELAY 基元与之关联。不过,由于IBUFDS_DIFF_OUT 缓冲器从 LVDS 对的两个不同 IOB 提供两个输入信号副本,而这两个比特流副本可经不同的 IDELAY 基元分别发送,这致使它们有不同的延迟量。IBUFDS_DIFF_OUT的 P 侧提供的比特流真实副本被与其关联的 IDELAY 延迟八分之一个位周期。用于IBUFDS_DIFF_OUT 反相输出的 IDELAY 设置为零延迟。这两个 IDELAY 模块提供两个不同的比特流“相位”。过采样器用两个时钟相位的双沿对这两个比特流相位分别采样,所以每个位周期可采集比特流八次,如图5 所示。

乍看似乎奇怪的是,标为有零相移延迟的数据其实是来自有八分之一位周期延迟的 IDELAY 模块,而标为有 45 度相移的数据却是来自有零延迟的 IDELAY 模块。但这是正确的。图5 中的CLK0 说明了这一示例。比特流的两个相位均在 CLK0 的上升时钟沿采样。从有八分之一位周期延迟的 IDELAY 采集的样本代表比从有零延迟的 IDELAY 采集到的样本“早”八分之一位周期的输入数据。

还有一点可能看似奇怪的是,使用两个 IDELAY,却将其中一个设置为零延迟。但这样做是为了确保两个信号副本使用同等布线资源,从而尽量减轻数据信号两个相位间的歪斜。