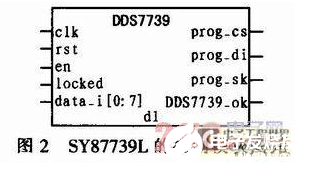

根据SY87739L的工作原理,可以用硬件语言编写出SY87739L的控制代码,图2是由Verilog代码用Synplify Pro8.1综合出的图元。

该模块控制SY87739L合成32 M频率功能仿真结果(由ModelSim SE6.1仿真)如图3所示。

测试文件中给DATA-I赋值为00000001,可以观察出prog_di串行输出的编程数据为0000_01100_01101_0100_000_10001_101_101;prog_cs在prog_di有效编程数据输出为高电平,待编程数据输出结束后回落到低电平:PROGSK输出SY87739L的编程时钟。经分析可以看出SY87739L控制模块可以实现预想的功能。

1.2 时钟提取芯片SY87700V的控制模块

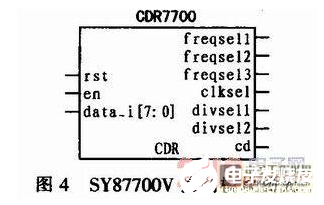

SY87700V对FPGA接收的数据进行时钟提取和数据恢复。将恢复的数据与接收端产生的本地伪随机序列进行对比,实现误码检测,两数据流对比时以提取的时钟为同步时钟。SY87700V在提取数据前要预知提取的频率的范围,此频率范围由FPGA发送给SY87700V。SY87700V的参考时钟是否进行分频,也要根据设置的参数由FPGA控制。此外该模块还要实现FPGA读取SY87700V的功能,以确定SY87700V是否完成时钟提取及数据恢复。根据SY87700V的工作原理,可以用硬件语言Verilog编写程序在FPGA实现控制SY87700V的模块,图4是由代码综合出的图元。

由FPGA控制SY87700V从122M数据提取时钟和恢复数据的功能仿真的结果波形图(用Modelsim仿真)如下图5所示。

测试文件中给data_i赋值为000011111,可以观察出FREQUSEL1输出值1,FREQUSEL2输出值为0,FREQUSEL3输出值为1,DIVSEL1输出值为0,DIVSEL2输出值为1。CLKSEL输出高电平(这一信号可以控制SY87700V完成提取的输入数据时钟的功能)。CD也输出高电平(使SY87700V能正常的进行数据恢复和时钟提取)。从图中可以看出SY87700V控制模块输出的信号可以控制SY87700V完成对122M数据的时钟提取和数据恢复,实现预想的逻辑功能。