发送的测试码为周期是29-1的m序列时,数据接收模块的仿真波形如图11所示。

在仿真文件中对该模块输入端口ser_i赋值一个码流,当赋值码流与本地伪随机序列同步的(同频同相),数据接收模块每比对一bit码,就在sum_o端口输出一高电平,若比对时有误码,则prt_o端口输出一高电平。在上图中,PRBS_r是本地合成的伪随机序列,可以看出该模块能够实现了m序列的产生和误码的检测和统计功能。

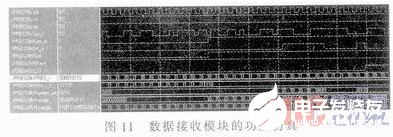

1.6 FPGA与单片机通信的控制模块

FPGA与单片机的通信控制模块(washbone moudle)实现的功能有:1)控制FPGA发送数据(总码数、误码数、误码块数)到数据线上;2)控制FPGA接收单片机发送到数据线上的控制数据。FPGA与单片机的通信控制模块将FPGA接收到的控制信息产生控制其他模块的信号,这些控制信号包括SY87739L频率合成的使能信号,SY87700V控制模块的使能信号,计数器复位信号,伪随机码的级数、速率、发送接收接口的控制信号等。由源程序综合出的图元如图12所示。

当SY87700V提取的数据频率为30.72 MHz时,SY87700V的参考频率为3.84 MHz。图13为FPGA与单片机的通信控制模块的功能仿真结果。该仿真是对washbone模块中控制FPGA接收单片机控制数据这一功能的仿真。在测试文件中RAM_data FPGA与单片机的通信数据信号赋值为0001010(控制该模块产生P09T_en、mb_OO_en、mb_OI_en为高电平的信号);exchange赋值高电平,既FPGA将数据(总码数,误码数,误码块数)存入FPGA的内部存储单元;FPGA GSn=0.WRn=1既FPGA读取数据线上的数据,并存入内部寄存器memory中。在该模块的输出管脚中:P09T _en、mb_OO_en、mb_OI_en输出为高电平,既控制伪随机发送模块合成9级m序列,发送、接收的端口类型都为光接口类型。从下列仿真图中可以判断该模块可以实现要求的逻辑功能。