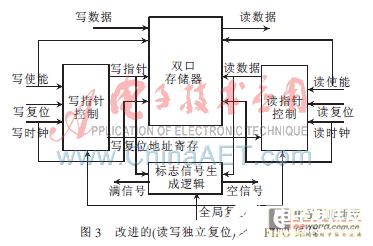

考虑到解嵌的音频信号可能存在丢帧、错帧,有的时候可能一块数据中并没有192帧的数据,而只是一部分数据,因此,在实际工作中需要利用块开始标志Z复位写地址指针。为了保证输出端也能在读地址复位的地方进行复位,保证输出的音频块与输入端对应,本设计提出了利用一个地址寄存器寄存写地址复位时的写地址,并利用该地址作为读地址指针更新参考,这样就增加了读取数据的可靠性。

图3是改进的(读写独立复位)异步FIFO结构。

3.2 设计仿真

系统设计时,利用Quartus II进行RTL级的逻辑设计并综合处理,然后设计仿真平台[5],利用Modelsim仿真工具对整个系统进行门级仿真。根据设计的异步FIFO 的工作特性,仿真平台对FIFO工作到满状态、空状态,以及写指针复位后的读操作进行了较全面的覆盖。

下面是测试平台的激励生成代码:

always #40 wr_clk=~wr_clk;

always #10 rd_clk=~rd_clk;

always @(posedge wr_clk) begin

if(!rstn) begin

wr_data《=0;

cntw《=0;

rd_en《=0;

wr_en《=0;

end

else if(cntw==400) begin

rd_en《=1;

cntw《=cntw+1;

end

else if(cntw==500) wr_rstn=0;

else begin

wr_en《=1;

wr_rstn《=1;

wr_data《=wr_data+1;

cntw《=cntw+1;

end

end

代码的功能是在较低的时钟速率下,先进行写操作,等到确保写满后(即计数达到400时),以高速的读操作来读取数据,并继续写数据。当计数到500时,对写操作复位,此时的复位地址是98。

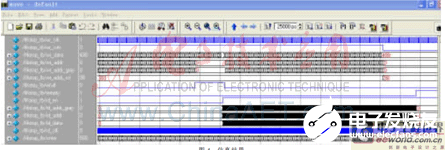

根据上述的改进方法,设计、仿真完成后,用Altera公司的Cyclone Ⅲ系列EP3C10E144C8芯片实现电路程序设计。仿真结果如图4所示。在图中可以看到,wr_addr_rst的值一开始默认为383,但写入端有写复位时,即为写复位时的地址值98,该值也即作为读操作的地址复位参考值传递到读操作模块。等到读操作进行第二轮读取并读到第98个地址时,再复位到0地址时,仿真完成。

本文基于FPGA内部存储器,提出了一种针对视音频解嵌系统更具效率的异步FIFO,对通用的FIFO进行改进,并利用硬件描述语言及相应的仿真工具实现了功能仿真。仿真结果表明,本设计能很好地按照设计的意图工作。此外,还针对视音频解嵌系统中,音频块输出端异步FIFO提出了写复位地址寄存,读地址根据此寄存值来进行更新及复位的改进,提高了异步FIFO的工作效率和可靠性。