2 系统软件设计

软件代码开发基于Altera公司的Quartus II 13.0平台,利用Verilog HDL语言实现代码块的设计与仿真。临空数据采集系统中,FPGA控制器内信号的性质和来源各式各样,有直接来自传感器的数字信号,有模拟信号转换后的数字信号,有程序内部的标志信号,有来自机载计算机的控制信号,有来自北斗模块发来的控制信号和定位信号,有FPGA控制器发出的数据信号、电机控制信号、电路板控温信号等。为了提高有效数据稳定地接收、存储和发送,需要对全体信号细致分类,这对程序代码模块划分有指导作用。系统软件设计要求代码可读性高、可靠性高、易维护、有可扩展的余地。系统设计的思路是先做总体架构,再逐个完成子模块的编写,最后在顶层模块完成信号连接。模块化的设计思路使得系统仿真测试更容易,代码维护性更强。

2.1 程序顶层架构

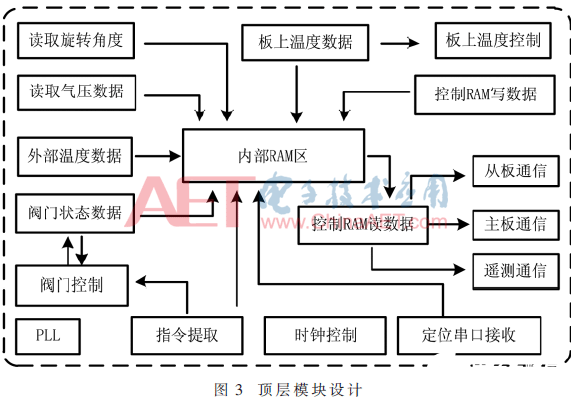

程序顶层模块的设计影响全局,关系到系统的稳定性和可靠性。系统结构的设计是根据模块的功能划分,每一个模块实现一个具体的功能,数据信息的交互通过各模块的输入输出接口连接。

数据采集系统信号比较多,而且FPGA与机载计算机、北斗模块的通信按照既定协议交互数据,即定时发送采集系统的数据,不定时接收外部指令和状态信息,为了便于管理数据,在FPGA内开辟一块随机存储器(Random Access Memory,RAM),专门针对各种信号存储和读取,这种数据结构使FPGA内部数据共享更容易,也不易产生读写数据紊乱现象[6-7]。引用Altera公司提供的IP核配置RAM,经过事先估计并留有足够的余地,将RAM大小设置为512 B,读写地址线各9根,并设置读写使能控制端口。图3为系统的顶层模块架构,核心模块是RAM区的读写模块,温度、压力、电压、电流信号,以及来自机载计算机或北斗的指令、位置和状态等信号流入RAM区,而存储的数据需要从RAM区被读取,通过UART串口模块发送给机载计算机和北斗模块。

2.2 通信模块程序设计

通信模块借助UART串口实现双向通信。FPGA控制器向机载计算机和北斗模块发送数据帧,同时实时接收它们的指令与状态数据。控制器向两个RS422串口发送定位、主从板信息、状态等数据帧,定位数据帧包含来自北斗模块的定位信息,主从板数据帧囊括采集系统采集到的各类信息,状态数据帧含有北斗模块的状态信息。此外,控制器向两个RS232串口发送遥测数据帧和自检数据帧,遥测数据帧由遥测帧头、定位信息、主板或从板信息和遥测数据帧尾组成,自检数据帧包括自检信息的请求。同时,有3个UART串口实时接收来自机载计算机和北斗模块的指令和状态信息。程序运行时需要对各种数据帧频繁读写操作,如果程序设计不合理,很容易造成程序死锁或崩溃。鉴于串口数据的接收和发送没有紧密地耦合,程序内部将数据接收和发送分成两个子模块来设计,然后在顶层模块通过wire型变量连接。为了有效解决数据读写不紊乱的问题,设计状态机来合理使用RAM区资源,增强程序的稳定性。状态机的空闲任务会出现连接两个always块的使能信号,设计watchdog程序增强程序的鲁棒性。