2 硬件电路设计

2.1 FPGA逻辑控制模块

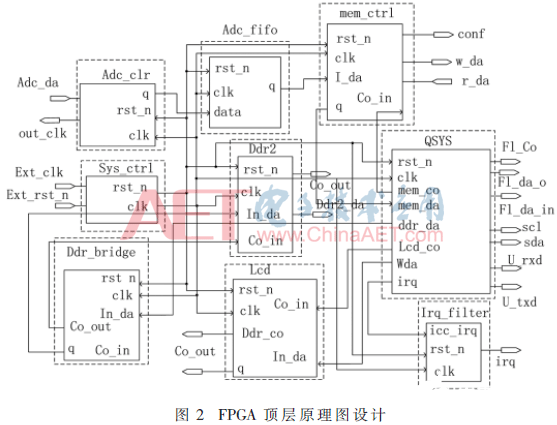

FPGA逻辑控制模块由ALTERA公司的EP4CE40F29C8N、EPCS64SI16以及海力士公司的H27U1G8F2B芯片组成。其中EP4CE40F29C8N为Cyclone IV系列FPGA芯片,该芯片最大时钟频率为472 MHz,具有533个IO接口,满足系统设计所需的最大时钟频率以及外设连接接口。逻辑控制模块由顶层设计部分、系统时钟与复位部分、采集控制部分、存储控制部分、LCD显示控制部分以及NISO II部分构成,其中顶层设计部分负责各个部分的连接以及逻辑控制模块与其他模块的接口。FPGA顶层原理图如图2所示。

在系统时钟与复位部分,由FPGA芯片系统时钟接口通过连接25 MHz无源晶振获得25 MHz时钟信号,通过“PLL”IP核将25 MHz时钟信号倍频为33 MHz、50 MHz、100 MHz以及200 MHz,以此作为系统的时钟电路。其次,产生异步复位同步释放的系统复位信号。

LCD显示控制部分由波形模块、数据缓存模块、LCD显示驱动模块和触摸屏指令接收模块组成。该部分提供接口将QSYS中的显示数据输出到DDR2缓存模块中;并为DDR2芯片和LCD显示芯片建立DMA通信机制,实现显示数据的输出。

通过QSYS系统集成开发工具建立NIOS II片上嵌入式处理系统,负责信号采集系统指令接收和程序执行控制。NIOS II系统完成以下工作:(1)系统初始化程序执行,监听LCD指令输入;(2)实现配置Flash芯片(H27U1G8F2B)的读写操作,配置Flash芯片中存放显示模块中的背景图片、字体库以及采集过程中采集批次编号和采集数据存储的起止位置信息;(3)实现采集数据读取操作,并将采集的信号数据转为波形显示数据;(4)负责系统各个外设驱动指令的输出。

2.2 模数转换模块

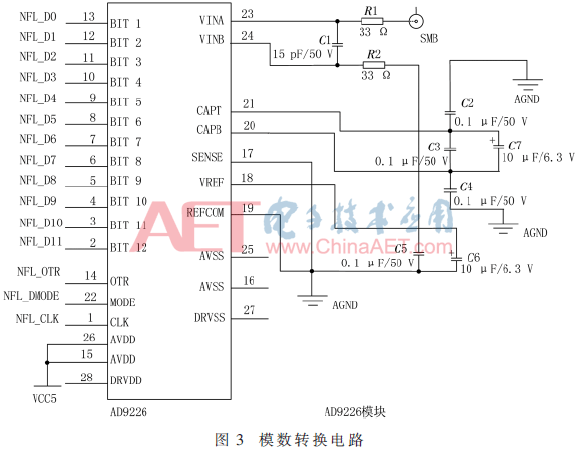

模数转换电路采用AD9226作为转换芯片,该芯片是一款低功耗(475 mW)、高精度(12 bit)的高速模数转换芯片,其最高转换速率为65 MSPS,并且具有良好的信噪比(70 dB)。本设计中,信号输入范围为1 V~3 V。该模块的采样时钟由FPGA逻辑模块提供,以达到对采样率的控制,本文中所有测试内容中采样率均为50 MHz,模数转换模块电路图如图3所示。

2.3 高速数据存储模块

为了匹配高速采样率,高速数据存储模块选取SLC颗粒的NAND Flash芯片[10]。本设计选择Micron公司的MT29F256G08AUCABH3芯片,该芯片在同步状态下,引脚读写速度可以达到200 MT/s,并且在数据写入过程中采用DDR模式,即在时钟的上升沿和下升沿均有数据写入。通过对其数据手册的分析,由于NAND Flash需要进行PROGRAM PAGE 操作,因此该芯片写入1页数据(8 KB)大约需要400 μs。在该时间段内,AD信号采集模块采集数据4×104 B,远大于NAND Flash存储数据,无法满足系统的设计需求。考虑到NAND Flash芯片在同步写入过程中加载8 KB数据需要40.96 μs,模数转换模块采集8 KB数据需要81.92 μs。影响系统存储时间的主要因素是NAND Flash的编程时间(350 μs)。