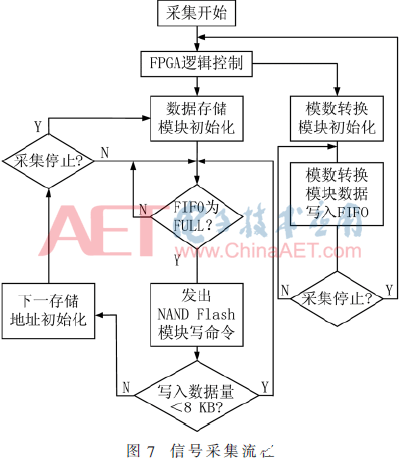

信号采集流程:

(1)高速存储模块初始化,对上一批次结束的所在LUN的下一个LUN进行存储状态激活。

(2)逻辑控制模块发送模式转换模块使能信号,同时向模数转换模块输入50 MHz时钟信号。

(3)模数转换模块开始工作,将输入的模拟信号以50 MS/s的转换率转换为12 bit的数字信号,并输出到逻辑控制模块。

(4)逻辑控制模块接收到12 bit后,将其左移4位与当前采集批次的4 bit二进制值相加产生一个16 bit存入FIFO中。FIFO设置为输入信号16 bit,频率50 MHz;输出信号为8 bit,输出信号频率为400 MHz;深度为4 096 words。

(5)当FIFO状态为“FULL”时,逻辑控制模块向高速数据存储模块发生写指令,向FIFO发送读指令,系统开始以DMA的方式将数据从FIFO中发送到高速数据存储模块。

(6)当完成page数据的存储后,逻辑控制模块关闭FIFO读使能。高速数据存储模块激活下一个LUN的存储状态,重复步骤(5)~(6)。信号采集流程图如图7所示。

3.2 信号采集停止流程

LCD显示模块中的“采集停止”按钮被触发,逻辑控制模块等待数据采集流程中步骤(6)执行时,关闭高速数据存储模块、模数转换模块使能,将当前采集批次编号和对应数据存储的起止位置存入配置信息存储Flash中。系统进入待机状态,监听LCD显示模块的指令输入,同时LCD显示模块初始化界面。

3.3 波形显示流程

LCD波形显示按钮触发后,界面切换到采集批次选择界面,通过点击选择对应批次的波形显示,进入波形显示操作流程。

波形显示流程:

(1)逻辑控制模块从配置Flash中读取相应批次数据采集的存储起止位置。

(2)读取高速存储模块中对应地址的数据,写入波形控制IP核中。波形控制模块负责控制LCD波形窗口控制,并将采集数据值锁存到双口RAM中,同时负责输出波形点显示坐标位置和波形显示时钟频率。

(3)将波形控制模块中的数据输入到LCD显示模块中的DDR2芯片中。

(4)LCD显示屏中,读取DDR2中的数据,进行显示。

(5)当对应批次的所有数据读取完毕后,波形显示流程结束。

3.4 高速数据存储控制流程

高速数据存储控制程序主要分为采集数据写流程和显示数据读流程。本设计中,采集数据写流程采用同步写入方式,工作频率为200 MHz;显示数据读流程采用异步读取方式,工作频率为50 MHz。

(1)高速数据写流程:①NAND Flash芯片激活同步读写状态;②从逻辑控制模块获取写入页地址;③向NAND Flash发送写操作命令;④向NAND Flash写入写操作地址;⑤NAND Flash等待数据写入使能;⑥接收到逻辑控制模块发送的写使能,开始写入数据;⑦当数据写满一页时,该LUN进入编程状态,同时从逻辑控制模块获取下一个LUN的存储地址,重复步骤③~⑦。