代码中寄存器level_contrl_TEMP存储level_contrl延时256个时钟周期后的信号,然后用level_eontrl_TEMP中存储的信号与level_co-ntrl的值相异或产生所需要的脉冲信号。

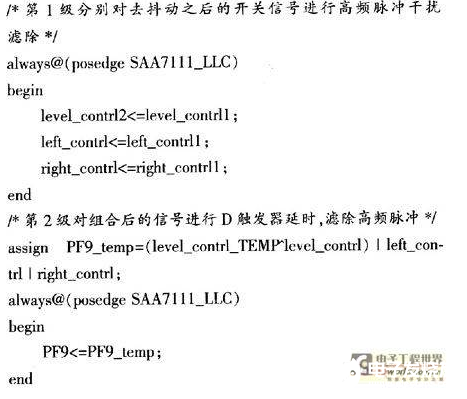

调试中发现,往抖动后的信号经常混有持续时间很短的高频脉冲干扰信号,因此设计中使用两级D触发器延时来彻底消除高频脉冲干扰,其程序代码如下:

2.2 双口RAM及开关信号编码设计

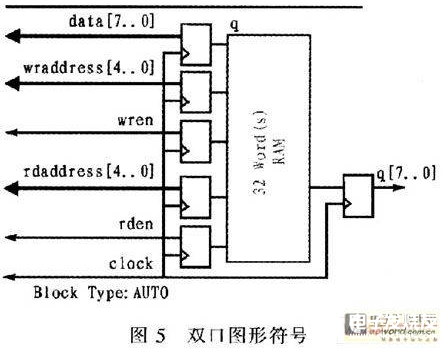

双口RAM分为真、假2种双口。真双口2个端口都可以读写,互不干扰。本次设计根据实际需要,添加的RAM模块一端只读,另一端只写,读写互不干扰。根据上述分析可知,开关控制信号只能知道有开关控制动作发生,但是不能识别具体哪个开关发生了动作。因此,设计中首先利用MegaWizardPlug_In Manager中的宏功能块RAM:2_PORT产生1个双口RAM存储块,然后对这个宏功能模块的参数进行适当调整,产生一个满足自己特定要求的模块,如图5所示。

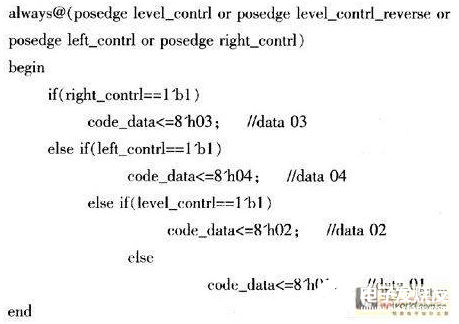

设计过程中,首先将开关动作进行编码。然后将编码后的数据存进空间大小为8的双口RAM中。当BF561检测到PF9上的脉冲后,在PF中断中读取RAM中指定地址的数据,然后根据这个数据进行开关状态解码并按解码后的控制信息对2块MAX4312器件进行操纵以控制视频通道。对开关动作进行的编码程序代码如下:

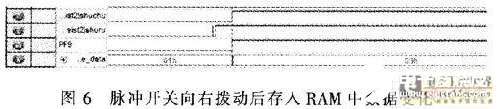

整个设计有4种开关动作,程序中分别将其编码成数据0l、02、03、04,然后将编码后的这4个数据存进双口模块中,等待BF561来读取并进行解码。图6是SignalTapⅡLogic Analyzer中对脉冲开关向右拨动后存进RAM中的数据进行采样。

程序中RAM的读信号rden_signal是由DSP发送的地址信号DSP_A、BANK选择信号DSP_AMSl以及DSP读信号DSP_ARE进行控制的。当DSP不从双口读取数据时,必须给DSP的数据线赋值高阻,以免影响SDRAM对DSP数据线的操纵。赋值指令如下:assignDSP_D=(rden_signal=l'b1)?DSP_D_TEMP;8 'hzz;其中DSP_D_TEMP是从双口中读取的数据。