2 码流播放器的硬件模块设计

使用FPGA实现了CY7B933和CY7B923芯片的功能,节约了大量成本;同时,用Cypress公司的USB2.0芯片CY7C68013A替代PCI或PCI-E接口,因为传输的码率较大,理论最大值为216 Mb,FPGA内部资源RAM资源无法满足要求,添加一个SDRAM作为缓存,缓冲数据,以免丢数。

另外,由于选择了低端的FPGA芯片,在编写版本FPGA程序时发现,其内部逻辑资源较少,无法装下实现ASI和SDI的全部功能程序,而且实际工程应用中并不需要同时实现ASI和SDI的功能,故添加了一个的CPLD,实现FPGA的PS模式的动态加载功能。

2.1 均衡器/驱动器

输入前端均衡器(Equaliser)选用的GS9064是第二代的双向性高速集成电路,均衡和恢复收到的信号(75Ω同轴电缆,速率从143 Mb/s到540 Mb/s),支持SMPTE 344 M和SMPTE 259 M标准,且270 Mb/s时性能最佳。具有自动检测线长并根据信号强弱自动匹配均衡的功能,也可根据特定需要设置均衡参数。

Driver选择CLC001驱动器,CLC001是集成高速电缆驱动器,可用来传输SMPTE 259M标准的串行数字视频和ITU-TG.703标准的串行数字数据(75Ω传输线,速率高达622Mb/s)。CLC001输出功耗小,十分适合长距离高速传输。

2.2 数据处理

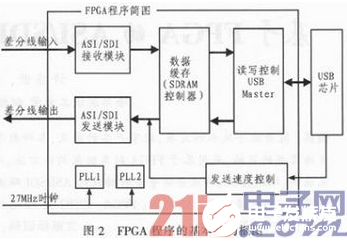

输入输出信号都经由差分线进入FPGA,出于成本的考虑,选择性价比较高的Altera公司生产的低端Cyclone I系列EP1C6F256C6。在FPGA内部实现ASI/SDI输入输出的控制,信号的串/并转换,码流分析,数据缓存(读写SDRAM),码流传输等功能。

因为TS流数据量较大,同样出于成本的考虑,选择在FPGA上外挂一个SDRAM,作为缓存(如果使用高性能FPGA,就可以使用FPGA内部RAM资源,但是成本较高)。FPGA程序的编写,尤其是控制SDRAM读写作为缓存的部分,是本设计的难点之一。

2.3 USB微控制器

FPGA控制的输入输出码流都经由USB2.0芯片传送至PC机。赛普拉斯半导体公司的EZ-USB FX2LP(CY7C68013A)是高集成、低功耗USB 2.0微控制器,将USB 2.0收发器、串行接口引擎(SIE)、增强型8051微控制器,以及可编程外设接口集成到一个芯片中,而且赛普拉斯研发出一个极具成本优势的解决方案,不仅能在极短时间内完成从立项到投放市场的过程,而且其低功耗特点使得总线供电应用成为可能。

3 码流播放器的软件设计

码流播放器软件系统主要包括以下4个部分。

3.1 FPGA程序功能模块

如图2所示,系统输入时钟为27 MHz,由两个PLL锁相环倍频得到270 MHz,135 MHz和两个相位差90度的337.5 MHz时钟。其中270 MHz是为ASI Transmitter提供,其余3个均为ASI Receiver所需。