1.2 节点升级原理

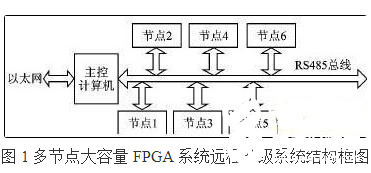

各个节点通过 RS485 总线与主控计算机相连,在无升级数据时,总线可以用来传输主控计算机对各个节点的查询和控制命令。主控计算机与各个节点的通信协议可以采用具有查询控制帧、应答帧和数据帧 3 种帧类型的协议。只有主控计算机可以发送查询控制帧,查询或设定各个节点的远程升级状态或工况信息。子节点接收主控计算机的命令和数据,发送应答帧,并完成自身的升级。

2 子节点的硬件设计

2.1 子节点硬件结构框图

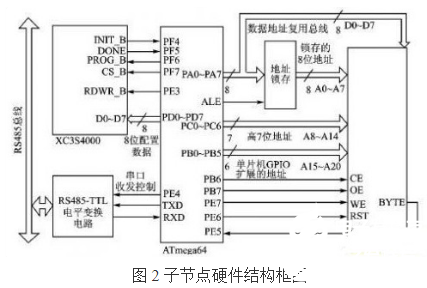

如图 2 所示,以一个由 Xilinx 公司的 XC3S4000 大容量 FPGA 构成的系统为例,远程升级系统子节点的硬件电路主要包括: ATmega64 单片机,用于存储大容量 FPGA 配置数据的 Flash,以及接入 RS485 总线的半双工总线收发器。ATmega64 单片机用于实现对大容量 FPGA XC3S4000 的加载,以及从 RS485 总线接收 FPGA 的升级数据并写入拥有 2 MB 存储空间的 Flash 存储器 SST36VF1601C 中。RS485TTL 电平变换电路采用 RS485 收发器 SP485R。

2.2 子节点硬件设计说明

在子节点的硬件设计中,ATmega64 单片机是实现整个升级功能的关键。ATmega64 是基于增强的 AVR RISC 结构的低功耗 8 位 CMOS 微控制器。由于其先进的指令集以及单时钟周期指令执行时间,ATmega64 的数据吞吐率高达 1 MIPS/MHz,从而可以缓解系统在功耗和处理速度之间的矛盾。AVR 内核具有丰富的指令集和 32 个通用工作寄存器,并且所有的寄存器都直接与算术逻辑单元(ALU)相连接,使得 1 条指令可以在 1 个时钟周期内同时访问 2 个独立的寄存器。这种结构大大提高了代码效率,并且具有比普通的 CISC 微控制器最高至 10 倍的数据吞吐率。ATmega64 有如下特点:

① 64 KB 的系统内可编程 Flash(具有同时读写的能力,即 RWW),2 KB 的 EEPROM,4 KB 的 SRAM,32 个通用工作寄存器;

② 53 个通用 I/O 口线;

③ 实时计数器(RTC);

④ 4 个具有比较模式与 PWM 的灵活的定时器 / 计数器(T/C),具有片内振荡器的可编程看门狗定时器;

⑤ 2 个 USART,面向字节的双线串行接口(TWI),1 个 SPI 串行端口;

⑥ 8 路 10 位具有可选差分输入级可编程增益的 ADC;

⑦ 与 IEEE 1149.1 标准兼容的,可用于访问片上调试系统及编程的 JTAG 接口。