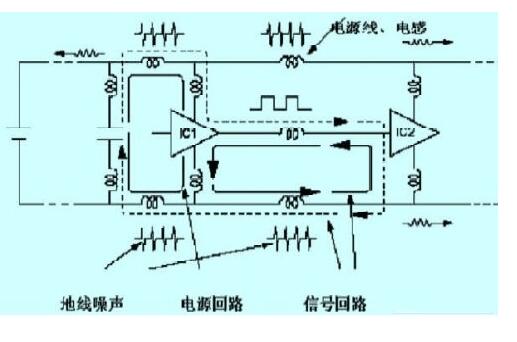

图1 各个电路阶段噪声的产生

2.3 PCB电路板上的敏感源

对于高速数字信号敏感源主要是指容易受到外部干扰的对象,例如:A/D、D/A 变换器,逻辑控制器,单片机,晶振,数字IC,弱信号放大器等。这些器件的稳定性直接关系到电路板的系统工作的稳定性和工作精度,因此对于这些敏感源要做好相应的保护, 提高自身的抗干扰能力。

3 提高PCB 线路板抗干扰措施

3.1 减小耦合回路

减小耦合的主要方法是减小信号环路面积, 其中主要应该解决地线、电源、敏感信号源及板边的环路面积。

3.1.1 减小地线、电源耦合回路

地线阻抗是造成线路板上地线噪声的主要原因, 因此应该尽量减小地线阻抗, 可以采取地平面或网格地。

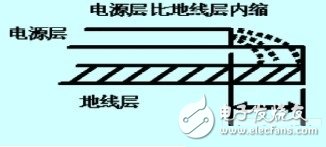

对于高速数字电路板应该采用多层板, 以减小环路面积, 将中间层作为电源或地层, 并且尽量保证电源与地相邻的层间距尽量小;让每一信号层都有一对应的地线层, 信号线与其地回路构成的环面积要尽可能小, 环面积越小, 对外的干扰越少。针对这一特点, 在地平面分割时, 要考虑到地平面与重要信号走线的分布, 防止由于地平面开槽等带来的问题,信号线不能跨越地平面和电源平面分隔区, 防止形成大的地线回路。同时电源层应该比地线层内缩3 m m 左右的距离, 这样将能够抑制70% 以上的电源干扰。如图2 所示。

图2 电源层比地线层内缩示意图

3.1.2 减小敏感源信号的耦合回路

对于敏感信号例如: 周期性信号, 如时钟信号、模拟信号、地址总线的低位信号等产生干扰较强, 也是设计高速数字电路的关键所在。印制板上关键信号布线应该按照从高到低的原则走线(排序方式:高到低 :模拟信号-复位信号-I2C- 时钟信号- 读写信号- 高速、射频信号- 数据总线- 地址总线);关键信号布线尽量走内层;并要配小电容并联进行滤波;信号层只有通过地平面隔离后的两个层, 才可以平行走线; 信号线应尽可能使其互连线最短; 印制板上高频连线的元件尽可能靠近走线短; 以减少高频信号的分布参数和电磁干扰, 这样才能够提高敏感信号源的抗干扰能力。

3.1.3 减小线路板边缘的耦合回路

印制电路板的板边处理是否合理, 决定着是否能够更加有效地抑制信号的对外干扰。为防止高速数字电路通过板边对外干扰, 应该严格控制其布线位置, 让其尽量靠近印制板内部。高频等干扰较强信号线不应该走到板的边缘, 以防止无对应地层耦合回路, 产生信号对外的干扰泄漏, 如图3 所示: