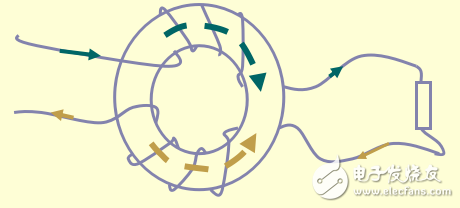

●共模电感的绕制

共模扼流圈中的负载电流产生的磁场相互抵销,因此磁芯不会饱和。

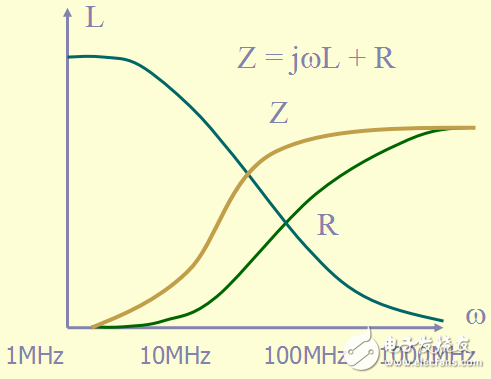

●磁珠阻抗

注意:共模电感和磁珠 需要测量温升!!

拓扑EMI 分析举例

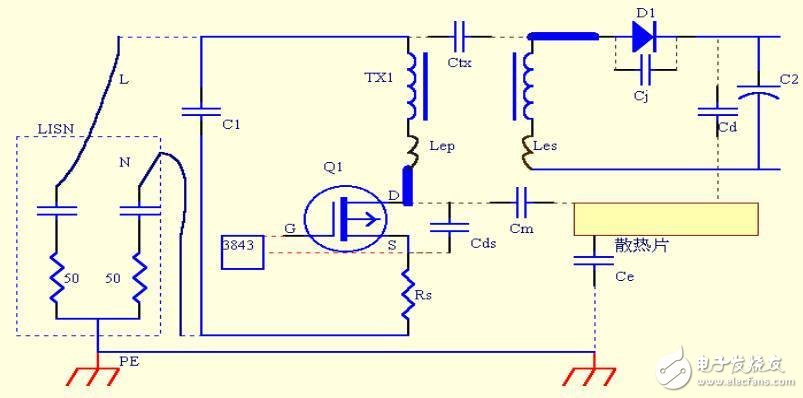

Flyback 架构EMI 分析

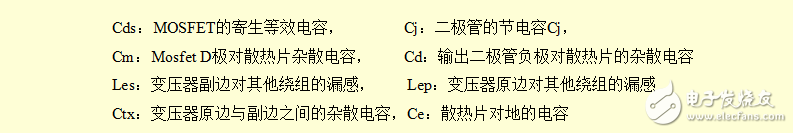

●Flyback架构的高频等效模型

●Noise 源:

大的di/dt和dv/dt 产生的地方,对Flyback架构来说,会产生这些变化的主要有:

★变压器TX1;

★MOSFET Q1 ;

★输出二极管D1;

★芯片的RC振荡;

★驱动信号线;

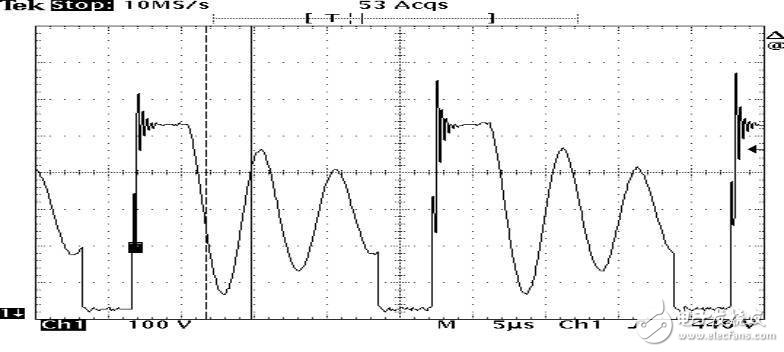

Q1 上 Vds 的波形

MOSFET 动作时产生的Noise :如 上图所示,主要来自三个方面:

①Mosfet开通、关断时,具有很宽的频谱含量,开关频率的谐波本身就是较强的干扰源。

②关断时的振荡 1产生较强的干扰。

③关断时的振荡 2产生较强的干扰。

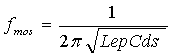

开关管 Q1关断,副边二极管D1导通时(带载),原边的励磁电感被钳制,原边漏感Lep的能量通过Q1的寄生电容Cds进行放电,主放电回路为Lep—Cds—Rs—C1—Lep,此时产生振荡振荡的频率为:

在Lep上的振荡电压Vlep迭加在2Vc1上,致使Vds=2Vc1+Vlep 。振荡的强弱,将决定我们选取的管子的耐压值、电路的稳定性。

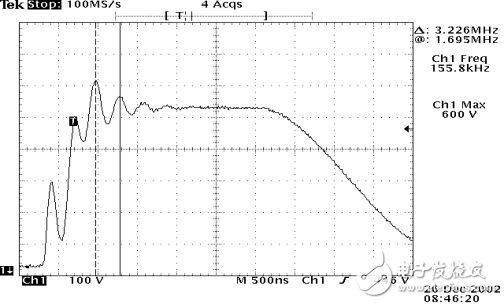

量测Lep=6.1uH, Q1为2611查规格书可得Coss=190pF(Coss近似等于Cds),而此充电板为两个管子并联,所以Cds=380pF 。由上式可求得f =3.3 MHz,和下图中的振荡频率吻合。

从图中可看出 此振荡是一衰减的振荡波,其初始的振荡峰值决定于振荡电路的Q值:Q值越大,峰值就越大。Q值小,则峰值小。为了减小峰值,可减小变压器的漏感Lep,加大Cds和电路的阻抗R。而加入Snubber电路是 极有效之方法。