今天小编要和大家分享的是八进制计数器,计数器相关信息,接下来我将从八进制计数器设计方案汇总(四款模拟电路原理实现过程),试用4位同步二进制加法计数器74161采用置数法构成十进制计数器 二这几个方面来介绍。

试用4位同步二进制加法计数器74161采用置数法构成十进制计数器 二

本文为大家带来四个八进制计数器设计方案。

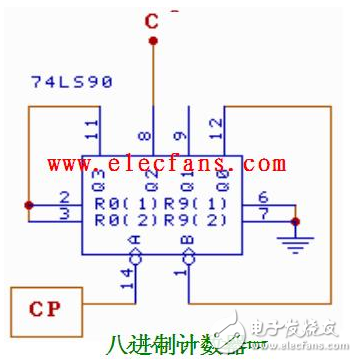

八进制计数器设计方案一:基于74LS90芯片的八进制计数器设计

详细电路设计方案:八8进制计数器

两位以上的数需要74LS90芯片级连,即低位芯片计数满后,低位的最高位作为进位,送到高一位芯片的CP端。

八进制计数器设计方案二:同步八进制加法计数器设计

时序电路的设计,就是根据给定的逻辑功能,设计其逻辑电路。设计步骤为:

a.拟定原始状态表或状态图:把设计电路的一般文字描述变成电路输入,输出和状态关系的说明,在此基础上,拟定原始状态表或状态图。

b.状态简化:原始状态中可能有有多余的状态,可用状态简化的方法将其消去,以得到最小状态表。

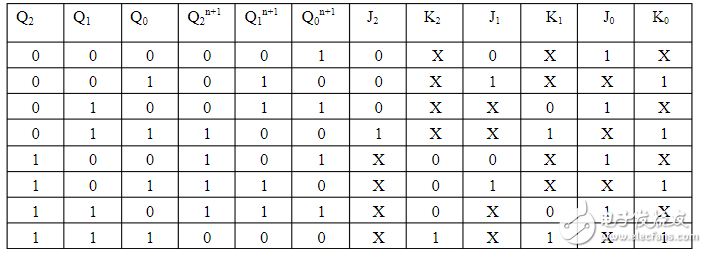

c.状态分配:根据最小化状态表的状态数目,确定构成电路的触发器数目。d.确定激励函数和输出函数:根据状态表确定。拟定状态表和激励表(如下表)

同步八进制加法计数器状态表

由上述表可求出方程:

J0=K0=1

J1=K1=Q0J2=K2=Q0Q1

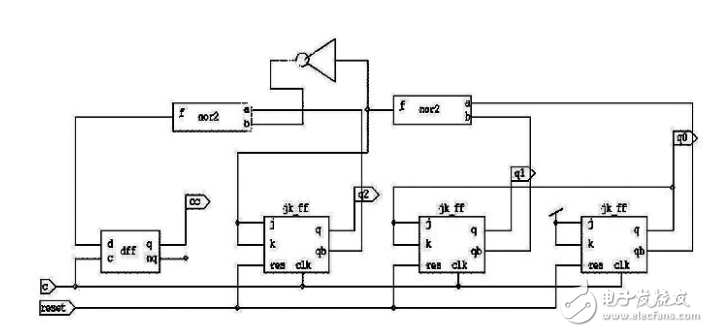

据方程得知我们所使用JK触发器的连接方式,其中根据J2=K2=Q0Q1可知道本电路需要用到一个与门电路,但因为与门电路要使用6个二级管,而或非门只需4个二极管,为了使用版图布线简单,我们把与门替换成或非门,并把两个输入端改成0Q1Q。当计数到“111”的时候计数器进行进位,输出C=1。而且此动作要与CP脉冲同步,此功能使用一个D触发器来实现。

同步八进制加法计数器的逻辑图

根据输入输出方程得出八进制加法计数器的逻辑图如下图:

同步八进制加法计数器逻辑图

逻辑图端口描述:输入控制信号:RESET,实现同步清零

输入时钟信号:CLK输出信号:Q0Q1Q2

输出进位端:C

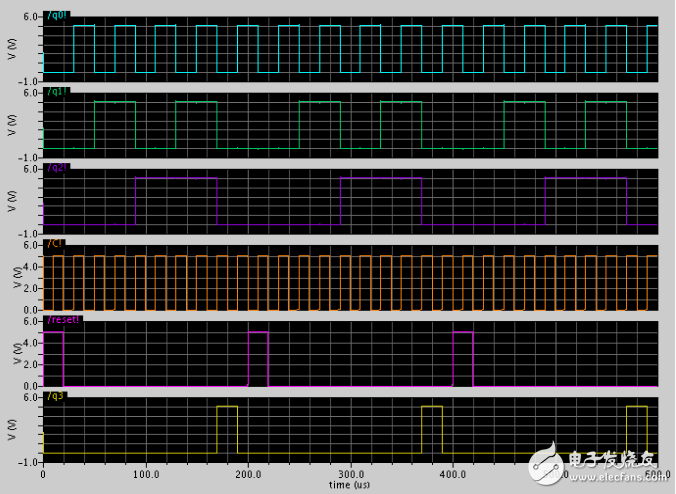

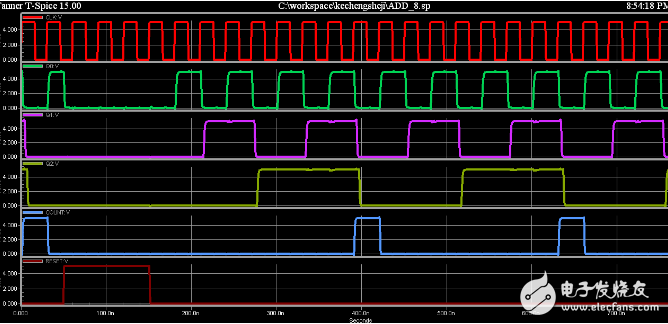

同步八进制加法计数器仿真波形

同步八进制加法计数器仿真波形图

(1)输出端用Q0Q1Q2表示,Q0为最高位,Q2为最低位,Q3是进位端,输出端用Q2Q1Q0表示;

(2)设计算器的初始状态为Q0Q1Q2=000,当第1个钟脉冲CP上升沿到来时,若Reset为1,Q2由“0”变为“1”,计数器的输出状态Q0Q1Q2由000—001;第2个CP脉冲作用后,Q2由“1”变为“0”,由于下降沿的作用,Q1由“0”变为“1”,计数器的输出状态Q0Q1Q2由000—001;依次类推,逐个输入CP脉冲时,计算器的输出状态按照Q0Q1Q2—000—001—010—011—100—101—110—111的规律变化。当输入第8个CP脉冲时,Q2由“1”变为“0”,其下降沿使Q1由“1”变为“0”,Q1的下降沿使Q0由“1”变为“0”,计数状态由111—000,完成一个计数周期。同时进位端Q3由“0”变为“1”。实现了同步八进制加法计数器的功能。

八进制计数器设计方案三:基于D触发器的异步八进制计数器设计

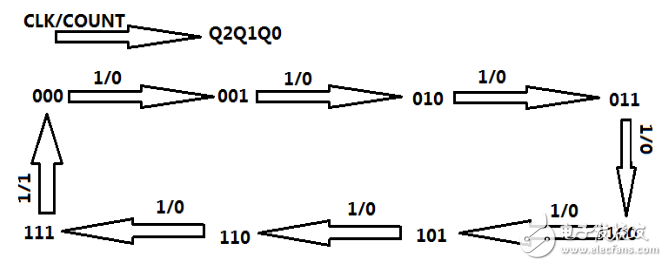

状态图以及激励表

按照要求,计数器的状态由时钟上升沿控制,从000到111共八个状态,其中从111状态跳转到000状态时count输出高电平。故可得出计数器的状态图如图下图所示。

八进制计数器状态图

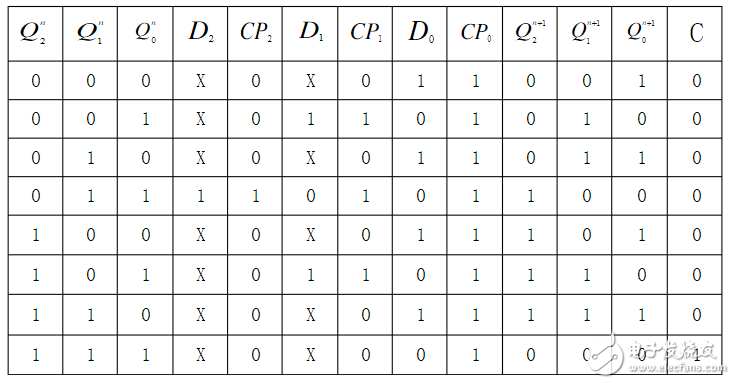

激励表如下表所示(注:表中Qnm为触发器输出信号,Dn为触发器输入信号,CPn触发器时钟信号,C为进位信号)。

异步八进制计数器激励表

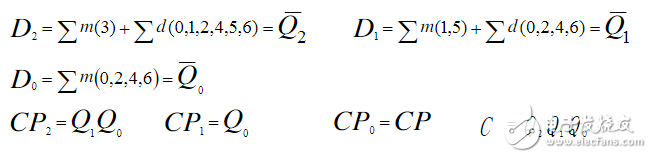

根据上表可写出激励方程和时钟方程

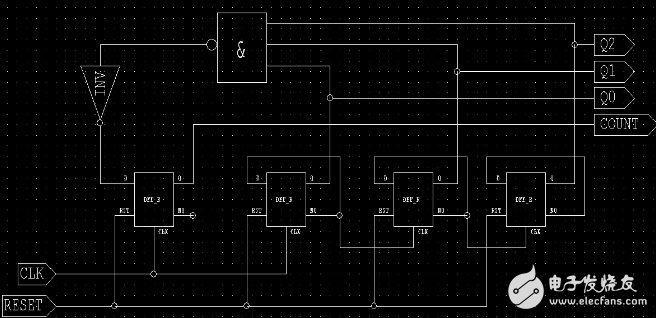

异步八进制计数器逻辑图

据方程得知我们所用的D触发器的连接方式,其中根据D2D1D0可知道本电路需要用到三个D触发器,而且每个D触发器的“非”输出都接到自身的D输入,时钟脉冲除第一级时钟接到时钟输入信号外其余的都接到前一级的“非”输出。当计数到“111”后计数器进行进位,输出C为“1”,而且此动作要与CP脉冲同步,则此功能使用三输入与门和D触发器来实现。

根据输入输出方程得出八进制加法计数器的逻辑图如下图所示。

逻辑图端口描述:

输入控制信号:RESET实现异步清零;

输入时钟信号:CLK输出信号:Q0Q1Q2;

输出进位端:count实现计数进位。

八进制计数器原理图仿真

八进制计数器仿真波形

如上图所示,当时钟上升沿到来时,输出信号岁时钟由“000”开始计数一直计到“111”,且当“111”变为“000”时仅为信号输出“1”。当清零端信号为高电平时不管时钟沿是否到来输出均为低电平。该结果符合设计目标。

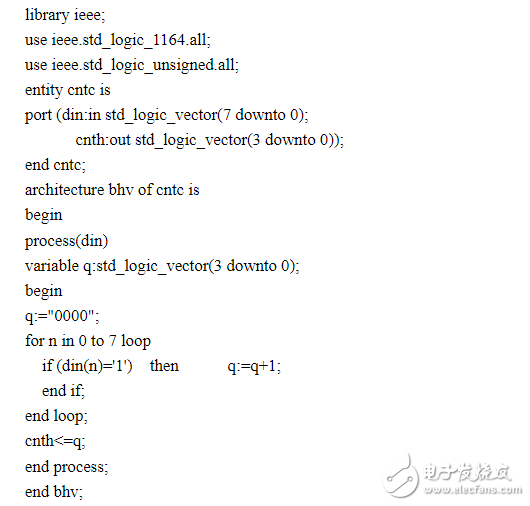

八进制计数器设计方案四:vhdl的八进制计数器的设计

关于八进制计数器,计数器就介绍完了,您有什么想法可以联系小编。