今天小编要和大家分享的是2进制计数器,计数器相关信息,接下来我将从2进制计数器设计方案汇总(五款模拟电路设计原理及过程详解),《4.同步二进制加法计数器.pptx》这几个方面来介绍。

《4.同步二进制加法计数器.pptx》

计数器是数字系统中用得较多的基本逻辑器件。它不仅能记录输入时钟脉冲的个数,还可以实现分频、定时、产生节拍脉冲和脉冲序列等。例如,计算机中的时序发生器、分频器、指令计数器等都要使用计数器。 计数器的种类很多。按时钟脉冲输入方式的不同,可分为同步计数器和异步计数器;按进位体制的不同,可分为二进制计数器和非二进制计数器;按计数过程中数字增减趋势的不同,可分为加计数器、减计数器和可逆计数器。

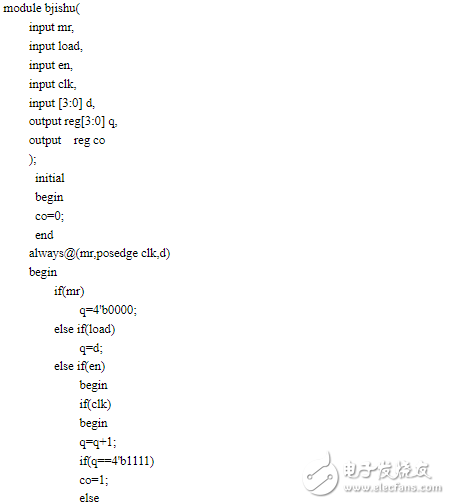

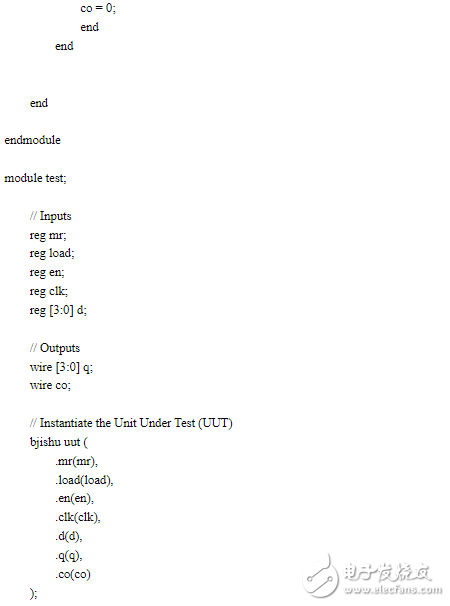

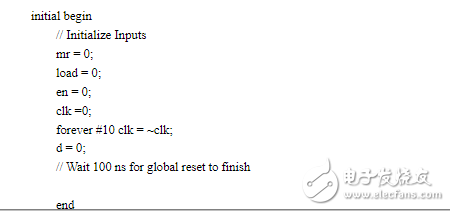

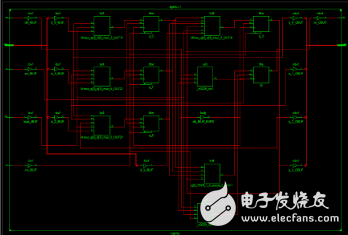

2进制计数器设计方案一

程序源代码

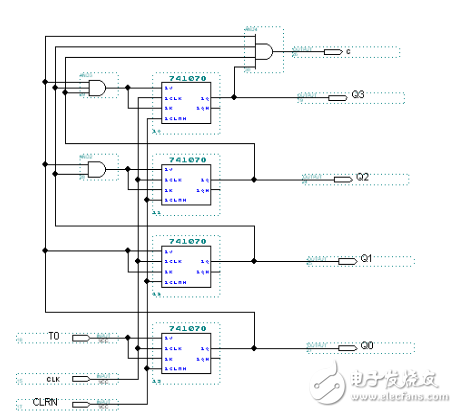

电路图

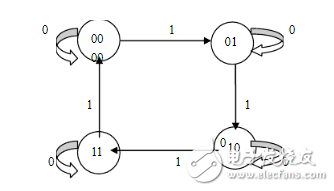

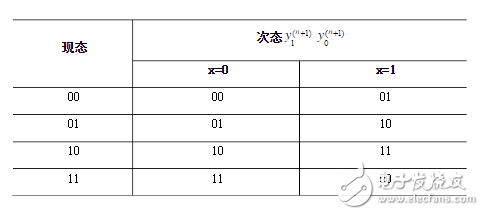

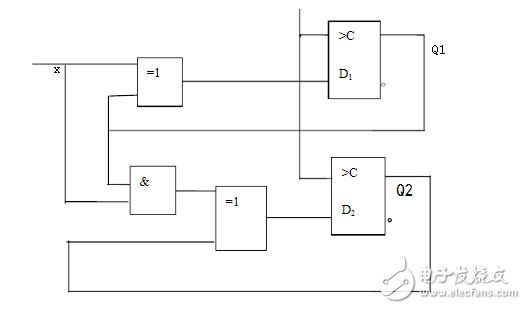

2进制计数器设计方案二

原始状态图

二位二进制计数器状态表

逻辑电路图

2进制计数器设计方案三

触发器构成的同步二进制加法计数器

触发器构成的同步二进制加法计数器

2进制计数器设计方案四

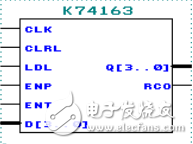

采用VHDL语言设计一个4位二进制计数器74163,它具有同步清零、同步置数、计数控制和进位输出控制功能。如下图所示。

4位二进制计数器74163

各端口功能

CLK:时钟信号,上升沿计数;

CLRL:同步清零端,低电平有效;

LDL:同步置位控制端,低电平有效;

ENP:与ENT同时为‘1’时,计数使能;

ENT:为‘1’时,可进行进位;

D[3..0]:计数器置数输入;

Q[3..0]:计数器状态输出;

RCO:计数器进位输出。

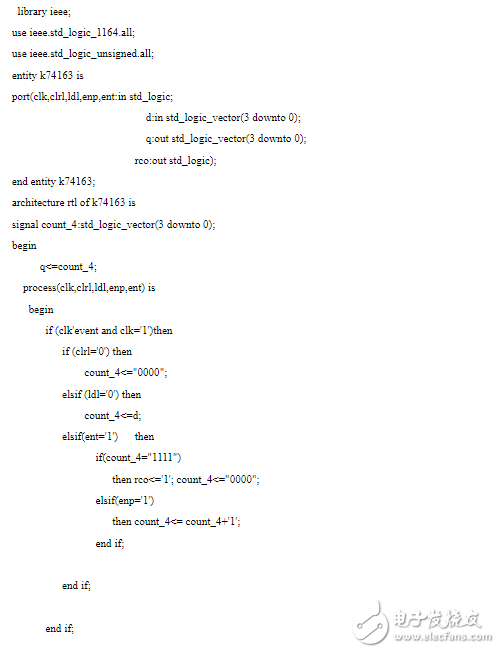

程序设计

2进制计数器设计方案五

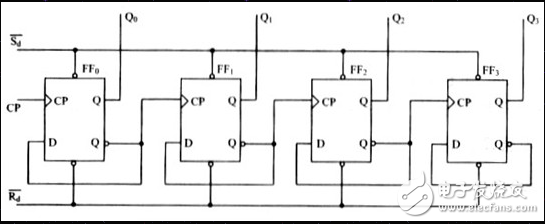

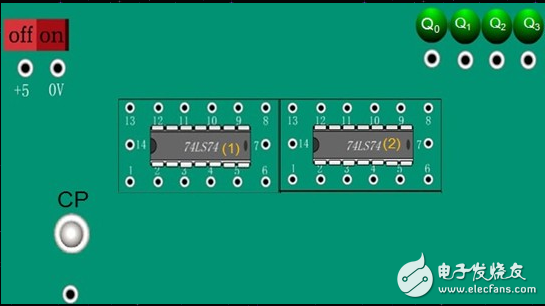

用触发器组成计数器。触发器具有0 和1两种状态,因此用一个触发器就可以表示一位二进制数。如果把n个触发器串起来,就可以表示n位二进制数。对于十进制计数器,它的10个数码要求有10个状态,要用4位二进制数来构成。下图是由D触发器组成的4位异步二进制加法计数器。

布线

1、将芯片(1)的引脚4、10连到一起,

2、将芯片(2)的引脚4、10连到一起,

3、将芯片(1)的引脚10和芯片(2)的引脚10连到一起,

4、将芯片(1)的引脚10连到+5V;

5、将芯片(1)的引脚1、13连到一起,

6、将芯片(2)的引脚1、13连到一起,

7、将芯片(1)的引脚13和芯片(2)的引脚13连到一起,

8、将芯片(1)的引脚13连到+5V;

9、将芯片(1)的引脚3接到时钟信号CP

10、将芯片(1)的引脚2、6接到一起,再将引脚2接到引脚11

11、将芯片(1)的引脚8、12接到一起,再将芯片(1)的引脚8接到芯片(2)的引脚3

12、将芯片(2)的引脚2、6接到一起,再将引脚6接到引脚11

13、将芯片(1)的引脚5、9分别接到Q0、Q1,再将芯片(2)的引脚5、9分别接到Q2、Q3

14、分别将两芯片的14脚接电源+5V,分别将两芯片的7脚接地0V。

关于2进制计数器,计数器就介绍完了,您有什么想法可以联系小编。